**CATRENE: GIVER and TAKER for 3D Innovation**

# SEMI's European 3D TSV Summit January 22nd 2014 Grenoble

# **SPTS Technologies**

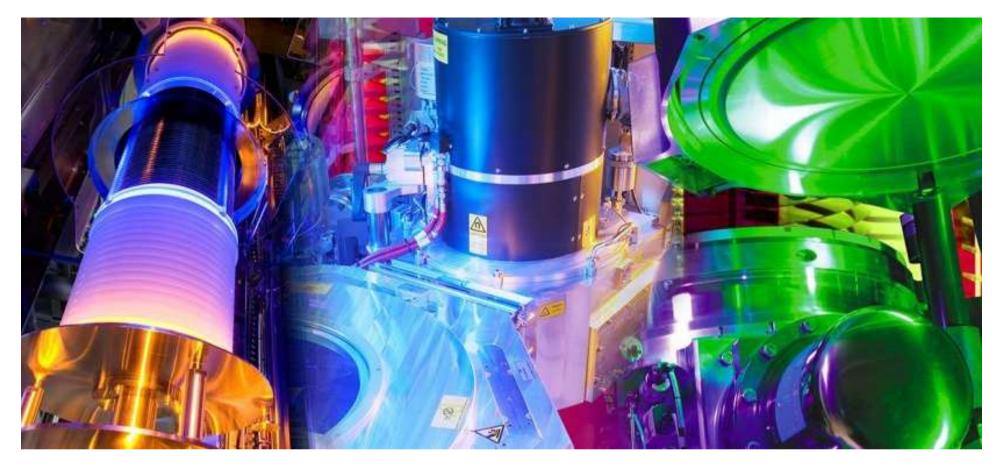

- SPTS Technologies designs, manufactures, sells, and supports etch, PVD, CVD and thermal capital equipment, providing advanced wafer processing technologies for the microelectronics industry.

- Formed in 2009, SPTS brings together over 40 years wafer processing experience from companies including Watkins-Johnson, Trikon Technologies, STS, Aviza Technology and AMMS.

- The solutions offered by SPTS include market-leading silicon etch, dielectric etch, dry-release etch, PVD, PECVD, APCVD and large batch vertical furnaces

- SPTS Technologies sas (France) is a subsidiary of SPTS technologies dedicated for sales, support & service, R&D.

# **SPTS Technologies**

- Broad supplier of wafer processing solutions

- For MEMS, compound semi, power and packaging markets

- Formed in Oct-09 via merger of former STS and Aviza

- MBO in Jun-11

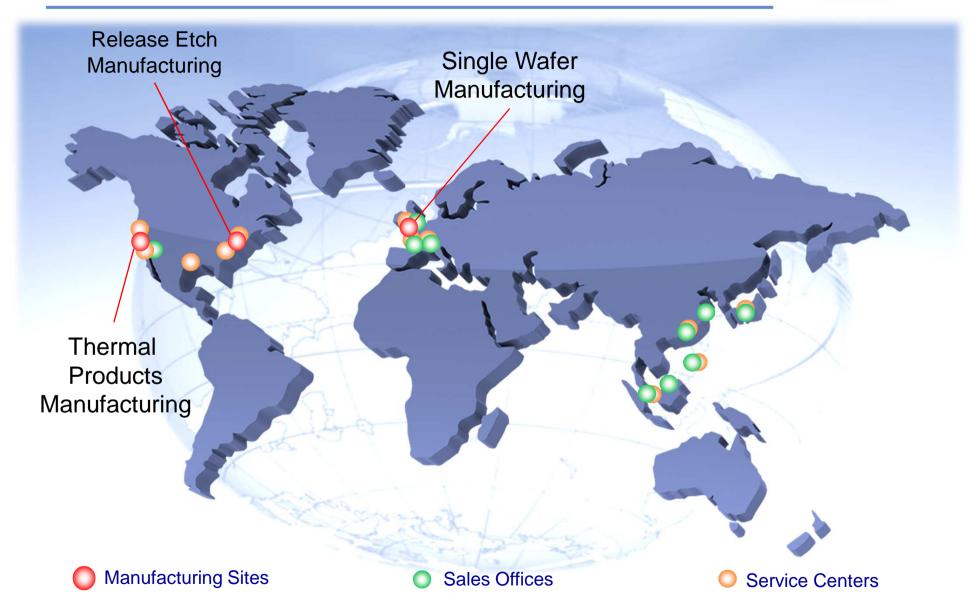

- Manufacturing sites in UK and US

- Global presence with 35 worldwide locations

Etch

PVD

CVD

Thermal

Release Etch

## SPTS - Global Presence

# **SPTS** Equipment is Used for Making...

#### **MEMS**

Micro Electro

Mechanical Systems

in inkjet heads,

smart-phones, games

consoles, and tablets

## **LEDs**

LED-backlit TVs, general indication, and automotive / industrial / domestic lighting

### **Power Devices**

Control / reduce / generate power used in electronic and power systems

#### **Semiconductor Devices**

Mainstream Si-based devices, including frontend CMOS/Logic/DRAM processing

## **Advanced Packaging**

Packaging semiconductor devices to reduce size and increase performance

## **High Speed Electronics**

Electronic devices using III-V materials to increase the speed /performance in devices

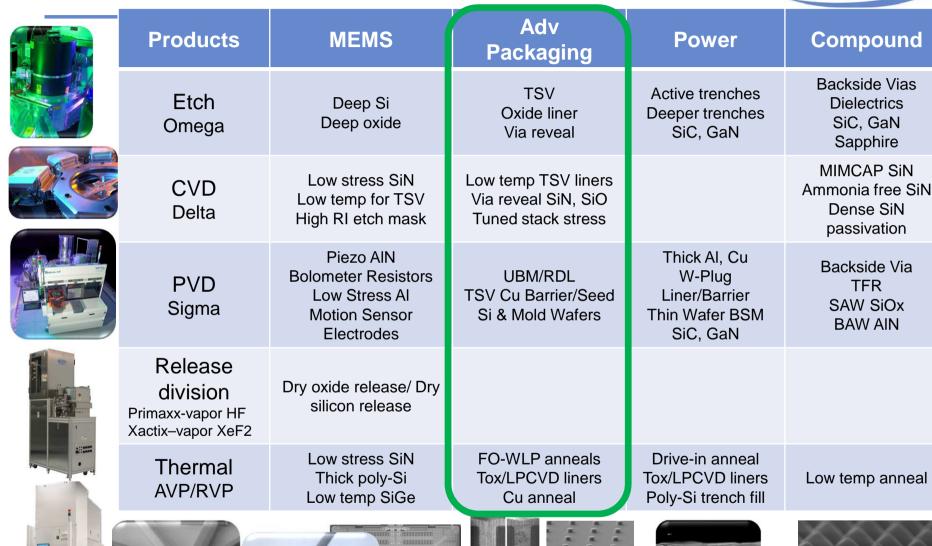

## **SPTS Solutions**

SPTS Technologies and is confidential. Any duplication, disclosure, distribution, dissemination or copying an that for which it is supplied is strictly prohibited, without the prior written consent of SPTS Technologies.

# **Single Wafer Products Division**

- Location

- Newport, South Wales, UK

- 104,200 sq ft

- 22 Universal Test Cells

- 15 Universal Assembly Cells

- 5S-Controlled Class 1000 cleanroom environment

- Flexible, multi-skilled workforce

- Lean culture with value-stream mapping

- Practice Design-for-manufacturing (DFM)

# **SPTS Product Strategy in 3D**

- Started with WLCSP in 2005

- 1<sup>st</sup> generation TSV, for CMOS image sensors

- Now used for fingerprint sensors

- Still highest volume TSV device

- Offering for 2.5 and 3D stacking

- Etch: Via etch and via reveal

- DCVD: Via isolation & via reveal

- PVD: TSV metals & bump/RDL

- Product strategy

- High productivity, low CoO.

- Film stability at low temp

- Running on...

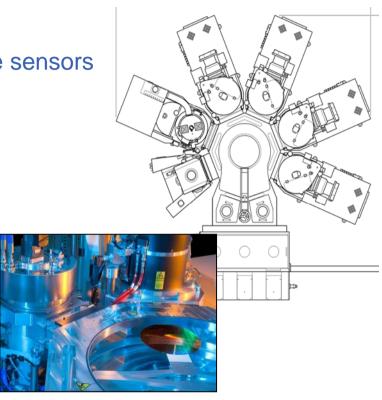

- Single technology systems

- Or multi-tech on one platform

# Versalis fxP VD\_etch and CVD on one pla

PVD, etch and CVD on one platform Ideal for R&D, pilot Saves capex \$\$ & floorspace

# **Projects contribution**

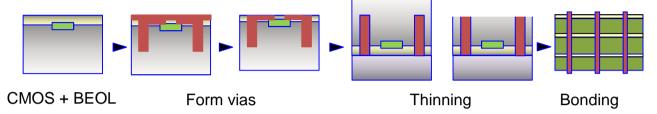

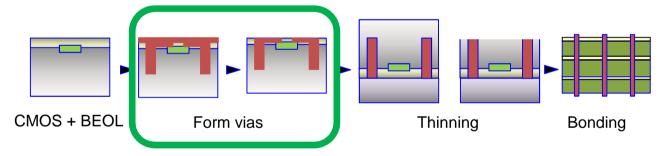

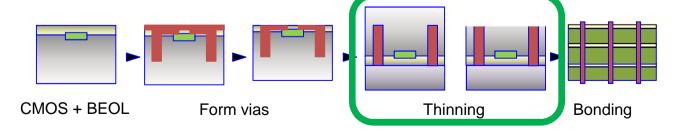

3D process flow

- SPTS contribution

- Vias : Etch, Deposition (insulation, Metal : barrier, seed)

Vias reveal

# **Projects contribution**

## CATRENE Projects

- COCOA

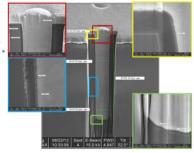

- 3D integration technology platform covering all processes required from vertical interconnects and robust bonding to innovative packaging to address new 3D products (6:1 & 20:1 A.R Vias).

Realization of product demonstrators for multimedia and wireless applications and sensor integration applications.

Protection membrane

## Master 3D

- 3D ICs with Through Silicon Vias (TSV) and Wafer Level Packaging (WLP).

- Tool enhancements to support high yield, mass production

- Functional and Final Test concepts

- Characterization and in-line Metrology methods development.

(60 x 120 um

# **Projects Collaboration & benefits**

- Direct discussion between all partners from R&D lab to end users

- Collaboration with labs :

- Validate concept & feasability of advanced recipes & hardware

- Collaboration with end users

- Define precisely process perf. specification

- Aim to demonstrate the robustness and stability of processes & tools

- Collaboration with other equipmeent Vendors

- Understand complete process flow specifications & limitations

# Why to chose CATRENE?

- Catrene offers to grant one part of the strategic R&D and product development

- Catrene offers an easy & free way of communication with all 3D actors from equipement vendors to IDMs

- Catrene offers us the possibility to demonstrate our tools & process capabilities for new technologies for IDMs on full demonstrators