# New possibilities offered by 3D

Ahmed.Jerraya@cea.fr

**Grenoble France**

www.cea.fr

leti & list

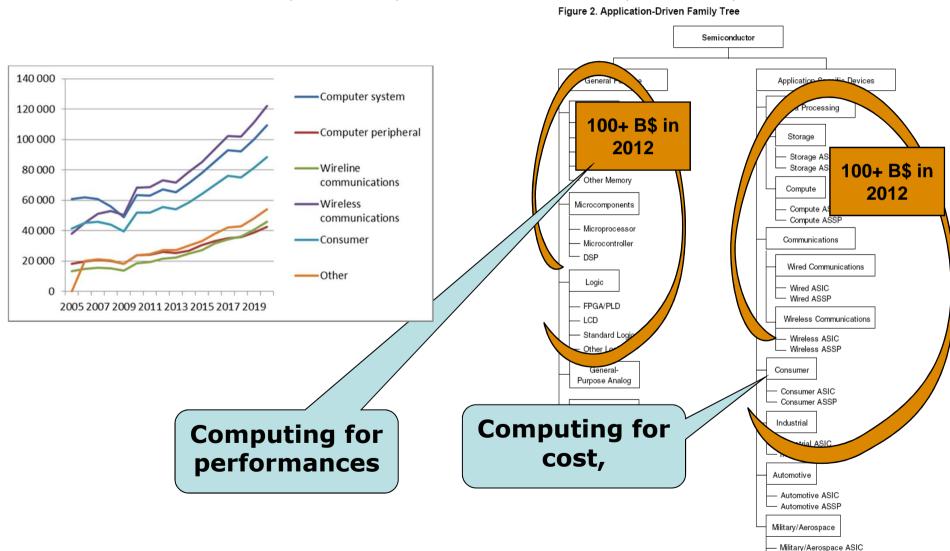

## Key message: 3D is impacting semiconductor markets

- IC markets are dominated by computing i.e Logic, Memory and I/O;

- The key challenges for future high-end computing chips are

Yield/Cost, power, data transfer and I/O, Heterogeneous Integration

- 3D is Happening

- To improve yield cost and power

- to shorten distances and increase bandwidth in a single chip, ...

But off-chip I/O will be the bottleneck. Si-Photonics will be soon required for chip to chip on board and later on Interposer (2.5D)

- To enable Heterogeneous Integration

- Implications on semiconductor will be disruptive

- The semiconductor Market

- 3 Top Trends in Semiconductors

- 3D to master Cost , Yield and Power

- 3D to master on chip and off chip Interconnect

- 3D to enable Heterogeneous Integration

- Implications on Semiconductor

#### **IC Market**

## From 270 B\$ (2012) to 460B\$ (2019) <IBS 2012>

© CEA. All rights reserved

Military/Aerospace ASSP

## **Computing Impacts larger Sectors**

| НРС    | 2005:<br>\$9,2B<br>2010:<br>\$14.2B | <ul> <li>HPC</li> <li>High End HPC Systems 25%</li> <li>Volume HPC Market, 75%</li> <li>Main Driver of Semiconductor<br/>Industry in 80's</li> </ul> |

|--------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC     | 2005:\$343B<br>2010: \$464B         | <ul> <li>PC-Desktop Market</li> <li>Driver of Semiconductor in 90's</li> <li>Introduced use of COTS</li> </ul>                                       |

| Embedd | ed 2005:\$577B<br>2010: \$896B      | <ul> <li>Embedded Market</li> <li>Introduced use of IP,</li> <li>Driver of semiconductor in 2000's</li> </ul>                                        |

|        | Future Computing                    | • Smart systems; IoT • New integration concepts • Driving semiconductor in 2010's                                                                    |

- The semiconductor Market

- 3 Top Trends in Semiconductors

- 3D to master Cost , Yield and Power

- 3D to master on chip and off chip Interconnect

- 3D to enable Heterogeneous Integration

- Implications on Semiconductor

#### Ceatech

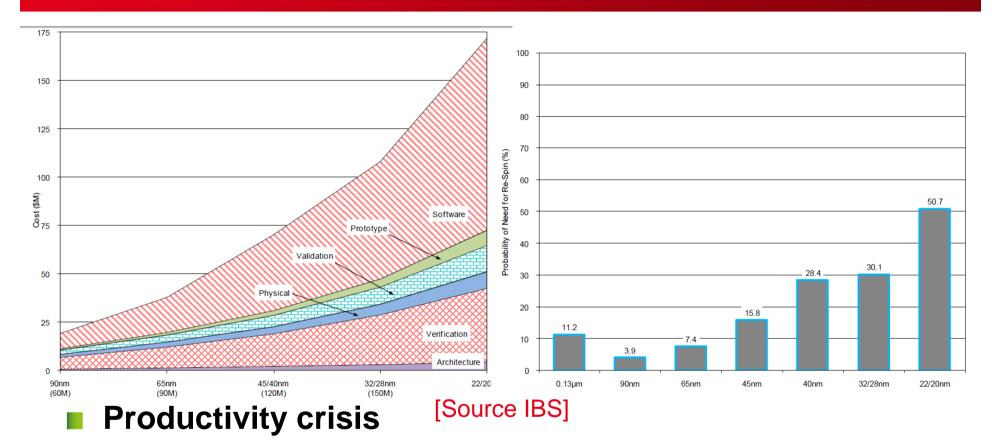

## The cost and yield challenges

- Design Cost is rocketing, 170M\$ 22 nm

- Time to Market Crisis for

- Design Respin rate reaching 50% for 22nm

### **Implications**

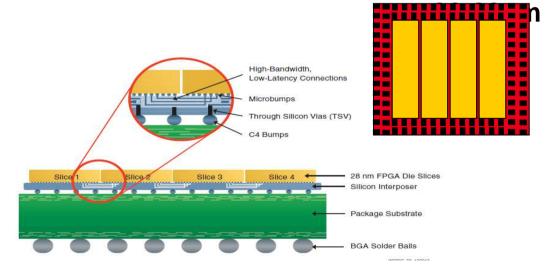

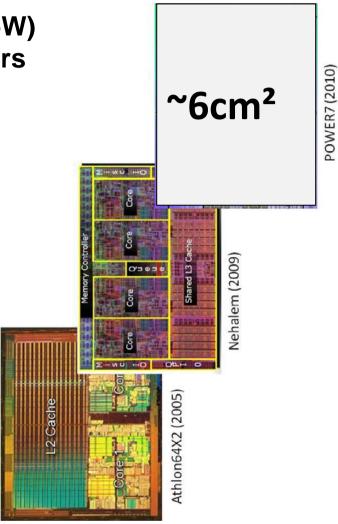

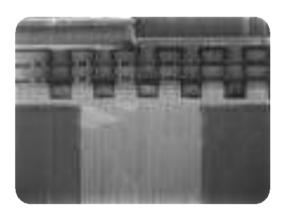

- The reticule Wall

- Maximum Integration on chip (6cm², 100+W)

- Main semiconductor manufacturing drivers

- High performances IC (CPU, GPU, FPGA)

The wall of Yield, cost, packaging ...

3D-IC Xilinx 28 nm

## 3D integration is happening

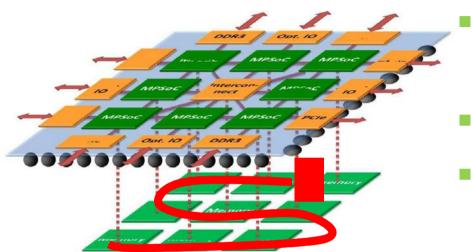

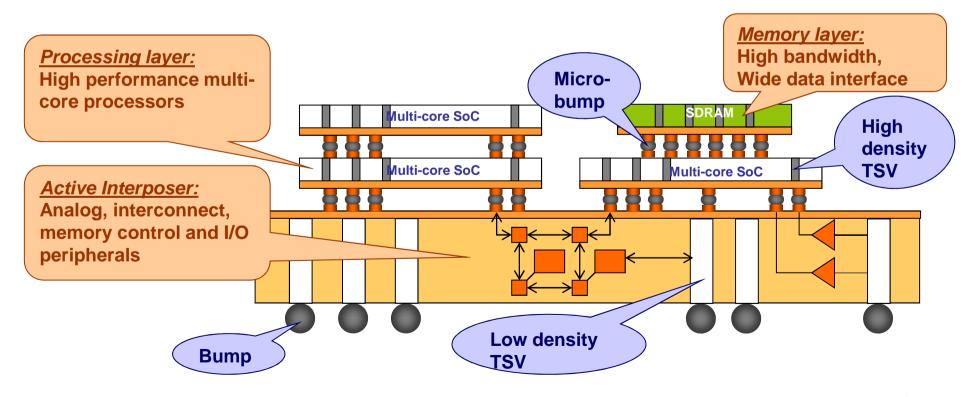

#### 3D SoC

- 3D-stacked dies

- Memory-on-processor:

- 3D memory hierarchy

- Processor-on-processor:

- Many-core cluster

- High bandwidth

- Fine grain architecture partitioning

- High density for vertical interconnects

- Face-to-back

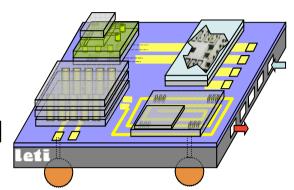

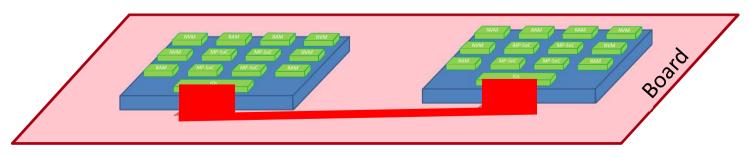

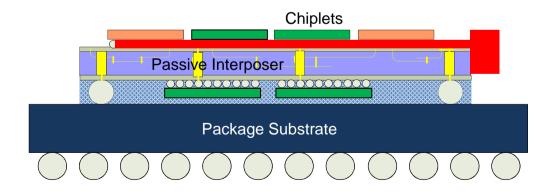

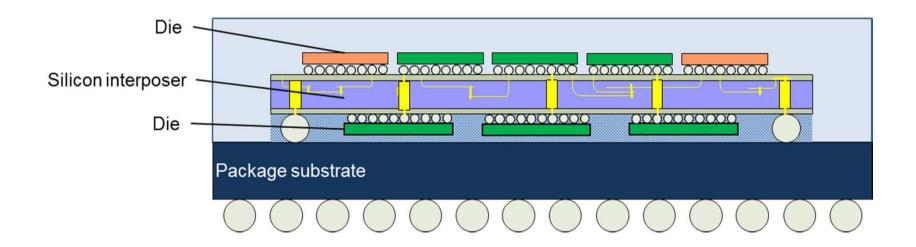

#### Silicon board

- Dies stacked on a silicon interposer

- Heterogeneous integration:

- Digital, analog, memory, input/output, power management

- Medium bandwidth

- System partitioning

- High density for horizontal interconnects

- Face-to-face

- Large size silicon interposer

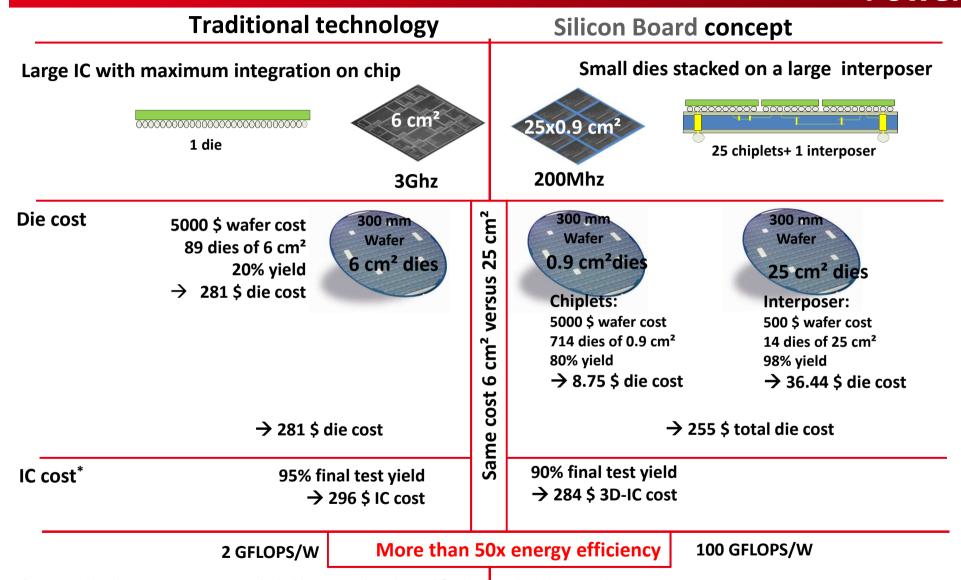

## Silicon Board concept to reduce cost and ...

**Power**

<sup>\*:</sup> test and package costs are not included but considered equal for both technologies in this exercise

- The semiconductor Market

- **3 Top Trends in Semiconductors**

- 3D to master Cost, Yield and Power

- 3D to master on chip and off chip Interconnect

- **3D** to enable Heterogeneous Integration

- **Implications on Semiconductor**

## **The Transfer Density Challenge**

Memory-interconnect density is becoming the bottleneck

|                                                                           | Cost for 1TBps memory bandwidth                                       |                                   |  |  |

|---------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------|--|--|

| Memory link, peak bandwidth and power consumption efficiency              | Number of data IO pins                                                | Interface<br>power<br>consumption |  |  |

| Multi-core SoC DDR3 DRAM 8.532 GBps 30 mW/Gbps                            | 3 800<br>Offchip                                                      | 240 W                             |  |  |

| 1066 MHz I/O bus clock, 32 bits, 1.5 V, Double Data Rate                  |                                                                       |                                   |  |  |

| Multi-core SoC LPDDR3 DRAM 6.4 GBps 20 mW/Gbps                            | 5000<br>Off-chip                                                      | 160 W                             |  |  |

| 800 MHz I/O bus clock, 32 bits, 1.2 V, Double Data Rate                   |                                                                       |                                   |  |  |

| Multo-core SoC Wide I/O DRAM 12.8 GBps 4 mW/Gbps                          | 41 000<br>Off-chip                                                    | 32 W                              |  |  |

| 200 MHz I/O bus clock, 512 bits, 1.2 V, Single Data Rate                  |                                                                       |                                   |  |  |

| >TBps 1 mW/Gbps  Assume 200 MHz 50K pins connected to SERDES to Photonics | 50 000 on chip +<br>40 Wavelengths<br>(or 40 Wave<br>guides) at 25Gbs | 8 W<br>+<br>MUX-<br>DEMUX?        |  |  |

## Why Si Photonics?

#### Si Photonics vs Electrical transfer

- Less energy than electrical-only (distance dependent)

- 10Mb/s , 1km: ADSL

- 10Gb/s , 1m: Inter Rack

- 100Gb/s, 10cm: Chip to Chip on (Silicon) Board

- 1Tb/s , 1cm: Silicon Board

- **Higher I/O bandwidth density**

- 3D accelerates Photonics Roadmaps

#### Ceatech

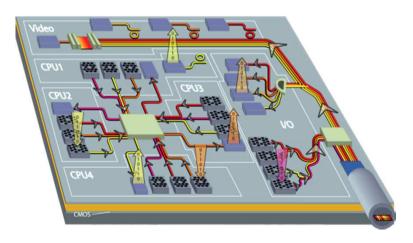

#### Data transfer Bottleneck for 1 TFLOP SOC

- 1 TFLOPs SoC / 10W doable in short tem (2014)

- Off-chip I/O (10Tb/s ) 1 TFLOPs => 1 TB/s

- Electrical solution:

- 5pJ/b @ 10Gb/s = 50 mW/b

- 1000 differential pin pairs 40W

- On Chip I/O

- Bisection wires: 50Tb/s

- Hitting the I/O density limit

- Silicon Photonics Solution is efficient at 1Tb/s/cm !!!!!!

- <10 cm Chip to Chip Optical Link required for SoC

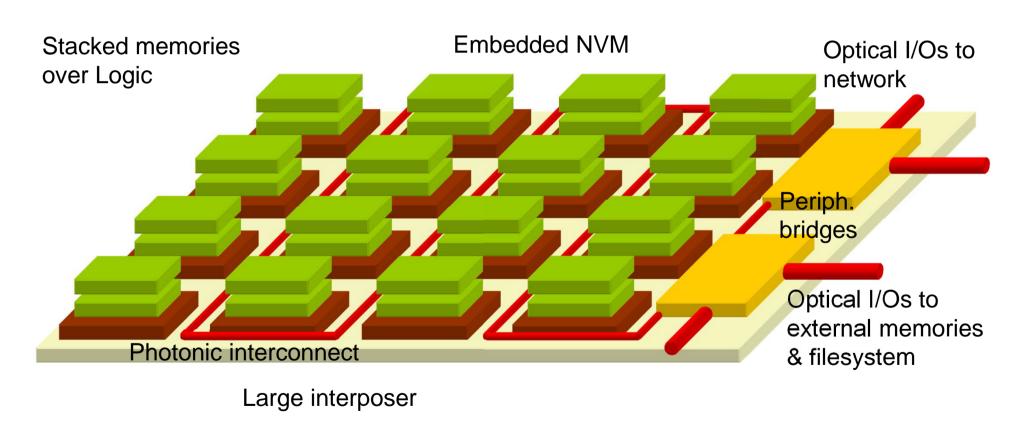

#### **More Integration in the Roadmap**

- 10 TFLOP SoC doable using Double sided Interposer

- Off-chip I/O 100Tb/s

- On Chip I/O

- Bisection wires: 50Tb/s

On Interposer Optical Link required for 10 TFLOP SoC

May require new Partitioning-architecture of the Photonic Link

- The semiconductor Market

- **3 Top Trends in Semiconductors**

- 3D to master Cost, Yield and Power

- 3D to master on chip and off chip Interconnect

- **3D** to enable Heterogeneous Integration

- **Implications on Semiconductor**

#### Silicon Board for Heterogeneous Integration

## Backbone for heterogeneous integration of small dies, passives and photonics $\rightarrow$ miniaturization

Interconnect with very low capacitive and inductive load

→ energy efficiency

#### Silicon Board for Heterogeneous Integration

- □ Heterogeneous integration rationale:

□ Digital logic shrinks significantly with process technology

□ Small dies shorten new process introduction and improve

- overall yield

- ☐ Analog design and IOs doesn't shrink a lot with process technology

- ☐ Short interconnect improves signal and power integrity

→ The SoC is partitioned into several dies, each of one being processed with the most relevant technology node in terms of performance and cost

- The semiconductor Market

- **3 Top Trends in Semiconductors**

- 3D to master Cost, Yield and Power

- 3D to master on chip and off chip Interconnect

- **3D** to enable Heterogeneous Integration

- **Implications on Semiconductor**

#### Implication of 3D on IC design

#### Contents of a single package:

#### Ceatech

#### Technology add-on

**Core 3D Technology** (200 & 300 mm)

**TSV** Cu Damascene line

**Bio Techno Modules** Biocomp,...

Leti

Thermal

management

modules

**Roadmap for Silicon Demonstrators**

Specific packaging solutions

Mechanical Stress

management

modules

(stress buffer,

compliant int.)

Dicing, direct-on-board, biocompatibility

**Stacking** Interconnects,

**Bonding Thinning RDL**

Bumps

TSV last

Modules for RF (integrated antenna)

**Today** 2012-2013 Demo

Si interposer

TSV Ø10μm, 50μm pitch

**Tomorrow** 2013

Memory on Logic

Logic-on-analog

Logic-on-logic (Advanced on Mature)

2015

Active interposer (NOC interconnect)

Next >2016

Modular and Stackable processor (NOC interconnect)

Cache memory on many core (3D network-in-memory)

Fine grain partitionning Pitch <10µm

Silicon on Flex Modules

underfill, P&P

**3D Technology Toolbox** 200 & 300 mm

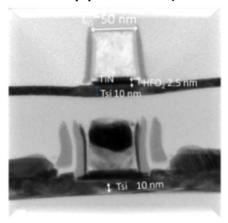

### Roadmap 3D TSV vs Monolithic 3D

#### TSV (3D Parallel)

- « back-end » solution

- Mixing of heterogeneous chips (function, node)

- Low-medium density (~um size via, ~10-100um pitch)

- Early introduction as stop-gap and/or low cost

#### **Monolithic (3D Sequential)**

- « front end » solution

- Logic-on logic

- Same node on different levels

- Heterogeneous material integration possible (III-V on Ge on Si ...)

- Ultimate density (same size and pitch of vias and contact as technology node of application)

#### Key message: why 3D is changing **Semiconductor markets**

- The key challenges for future high-end ICs are Yield/Cost, power, data transfer and I/O, Heterogeneous Integration

- **3D** is Happening

- To improve yield, cost and power

- to shorten distances and increase bandwidth in a single chip, ... But off-chip I/O will be the bottleneck. Si-Photonics will be soon required for chip to chip on board and later on Interposer (2.5D)

- To enable eNVM reducing static power consumption

- To enable Heterogeneous Integration

- Implications on IC design and then semiconductor markets will be disruptive

## Acknowledgement

- Design team: Fabien Clermidy, Denis Dutoit, Marc Belleville, José Luis Gonzalez, Pascal Vivet, Yvain **Thonnart**

- 3D Team: Severine Cheramy, Gilles Simon, Mark Scannel

- Silicon photonics team: Sylvie Menezo, Laurent Fulbert