Alan Mathewson, James Rohan and Cian O'Mathuna

# Background

- Heterogeneous Integration

- Possible Applications

- The Opportunities for Innovation

- Conclusions

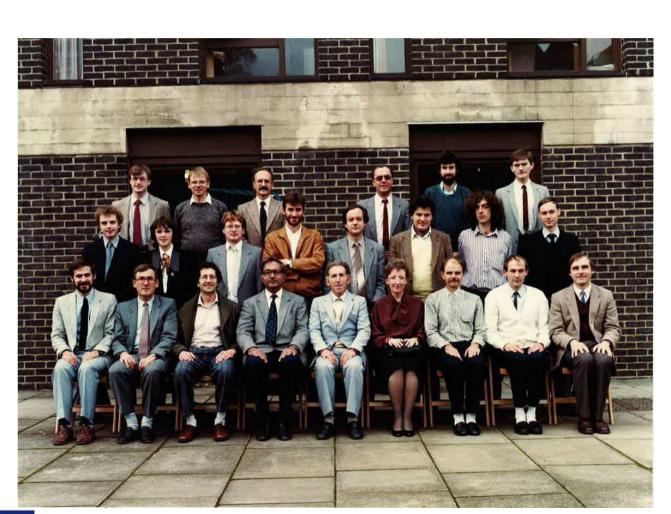

# • ESPRIT 245 ( 3DSOI - 1985-1988)

- 7 partners

- STM, CNET, CEA-LETI, Thomson CSF, U. Cambridge, GEC Research, NMRC (Now Tyndall)

**Europes First 3D Technology**

- Zone Melting Recrystalization (ZMR) of Si to form single crystal Si on top of SiO2 layers.

- Laser/ E-Beam ZMR

- Epitaxial Lateral Overgrowth (ELO) Selective Epitaxial Growth (SEG)

- 3D circuit Evaluation

- Device Design and Demonstrator

www.tyndall.ie

(1985)

#### The 3DSOI Consortium

www.tyndall.ie

### ESPRIT 245 Summary

- Stepper motor controller

- 'Mezanine' Structure- one layer of interconnect

- 50-70 V L-DMOS in Bulk, 3um CMOS Gate Array in SOI (40 um Seed window spacing)

- No thermal impact on DMOS Channel due to ZMR ( laser and e-beam ) LDMOS channel ( <1um)</li>

- Used SEG and ELO with a-SI to minimize stress at corners of seed layer and planarise structure

- Fully Stacked Inverter

- No problem for PMOS in bulk due to ZMR Process

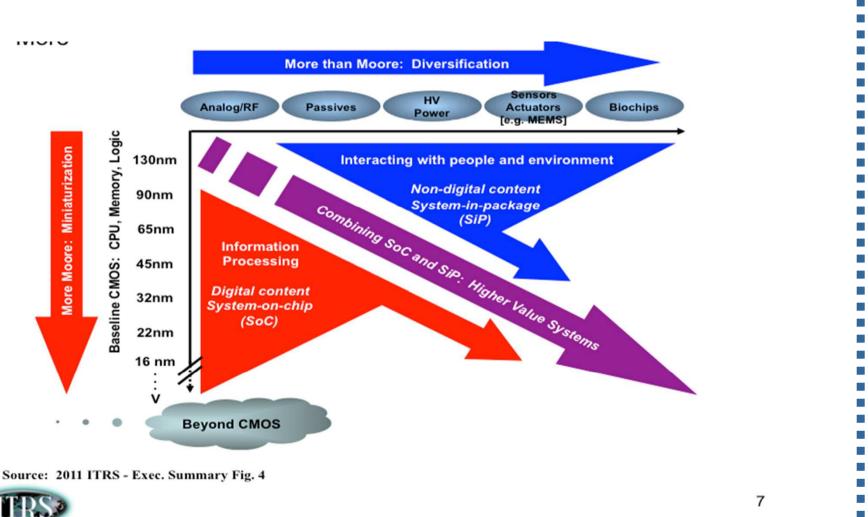

#### **Technology Evolution**

www.tyndall.ie

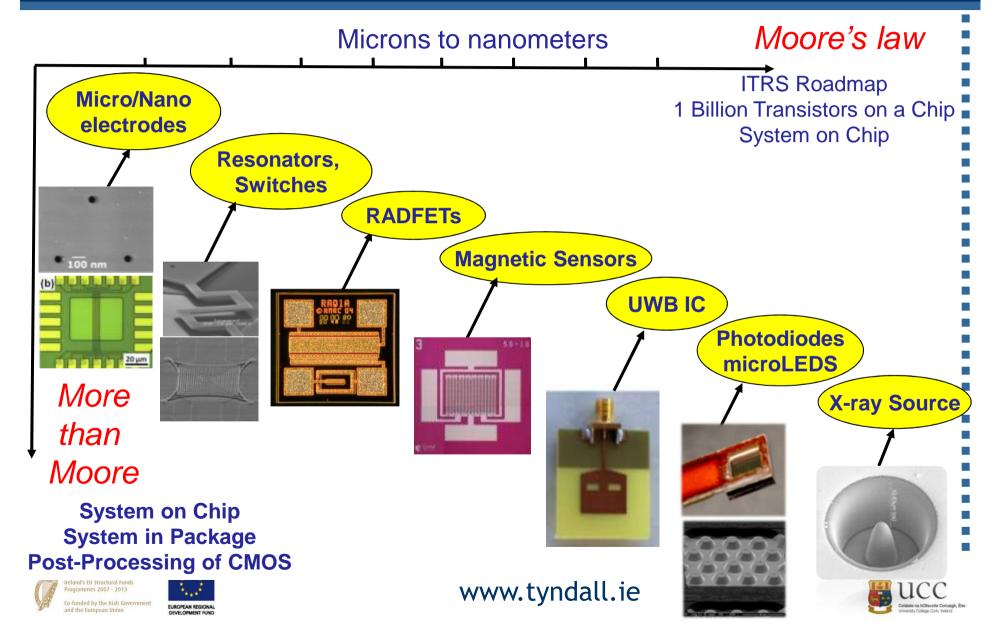

#### More Moore

#### - Sensors and Actuators

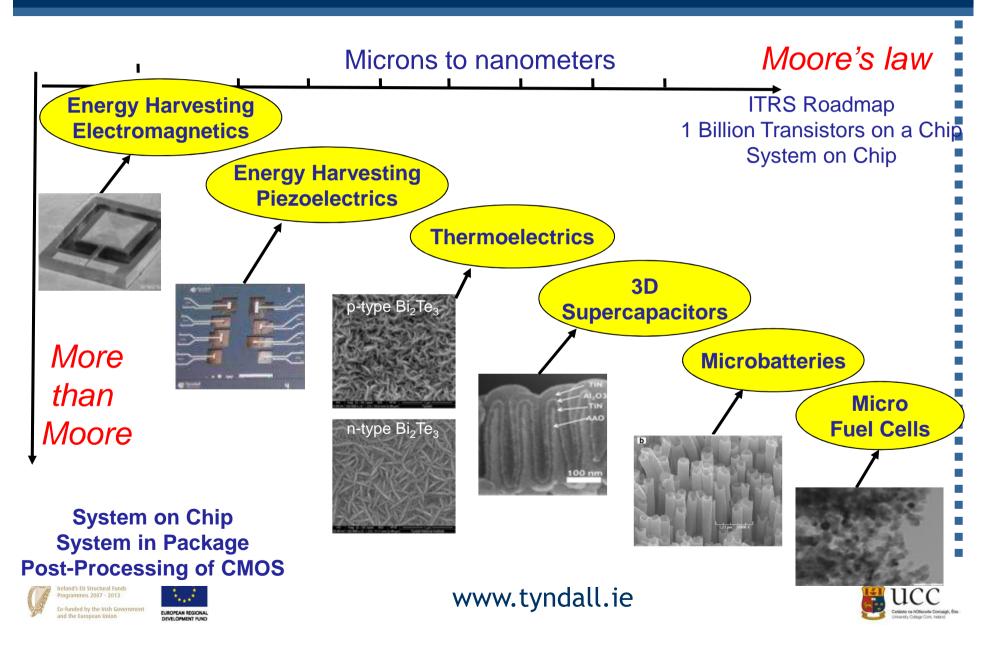

#### More Moore

- Integrated Energy Solutions

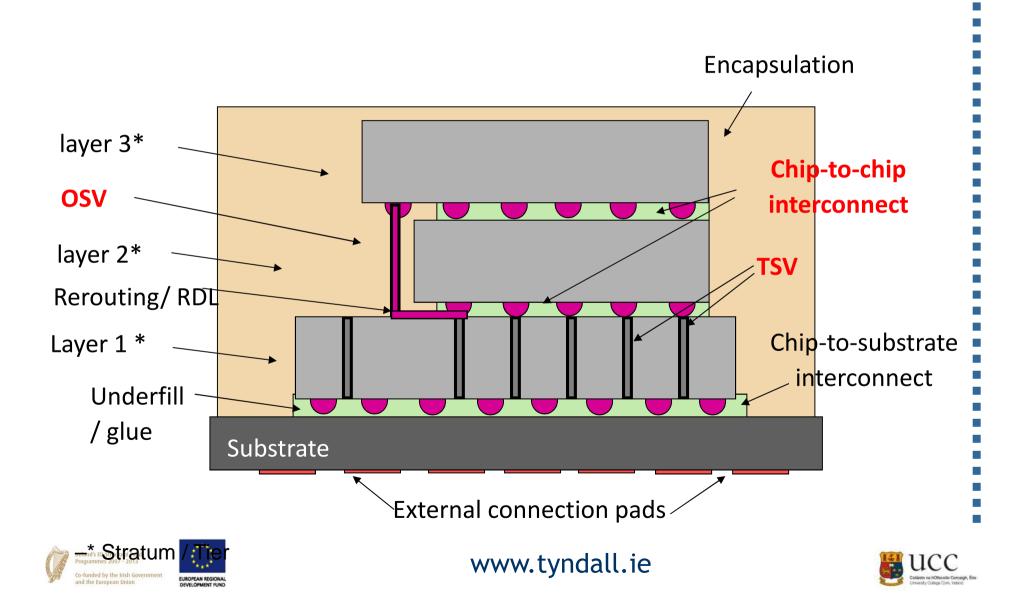

This 3D-TSV process is typically integrated in the Si-wafer fabrication line. The 3Dstacking process is generally done outside the standard Si-process line.

Table INTC7 Global Interconnect Level 3D-SIC/3D-SOC Roadmap Global Level, W2W, D2W or D2D 3D-stacking

|                          | 2011-2014     | 2015-2018   |

|--------------------------|---------------|-------------|

| Minimum TSV diameter     | <b>4-8 μm</b> | 2-4µm       |

| Minimum TSV pitch        | 8-16          | μm 4-8 μm   |

| Minimum TSV depth        | 20-50 µm      | 20-50 µm    |

| Maximum TSV aspect ratio | 5:1 - 10:1    | 10:1 - 20:1 |

| Number of tiers          | 2-3           | 2-4         |

Table INTC8 Intermediate Interconnect Level 3D-SIC Roadmap Intermediate Level, W2W 3D-stacking

|                          | 2011-2014  | 2015-2018    |

|--------------------------|------------|--------------|

| Minimum TSV diameter     | 1-2 µm     | 0.8-1.5µm    |

| Minimum TSV pitch        | 2-4 µ      | m 1.6-3.0 μm |

| Minimum TSV depth        | 6-10 µm    | 6-10 μm      |

| Maximum TSV aspect ratio | 5:1 - 10:1 | 10:1 - 20:1  |

| Number of tiers          | 2-3        | 8-16 (DRAM)  |

#### Chip Stack Nomenclature

## **FSV** Materials issues

| Higher aspect ratio fill<br>Barrier layer<br>Seed layer<br>Cu conductor                                                                                    | Significant issues<br>Cost<br>Speed<br>Reliability                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| <ul> <li>Improved barrier Layer</li> <li>Ability to process in high aspect<br/>ratio</li> <li>Plateable?</li> <li>Adhesion</li> </ul>                      | <ul> <li>Seed layer</li> <li>Adhesion</li> <li>Conductivity</li> <li>Stability in plating solution</li> </ul> |

| <ul> <li>Barrier fun</li> <li>Cu bottom-up fill</li> <li>On chosen seed/t</li> <li>High rate</li> <li>Additives required</li> <li>Decrease cost</li> </ul> | Darrier combination<br>d                                                                                      |

## Wafer scale Cu Plating (OSV)

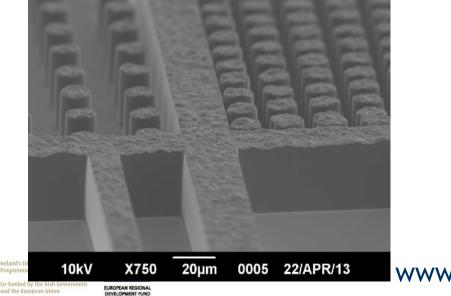

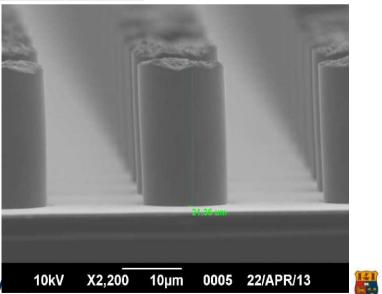

-Cu microstructures in wafer scale deposition using the Digital Matrix wafer plating tool.

-Pillars -12 μm diameter -22 μm height.

ucc

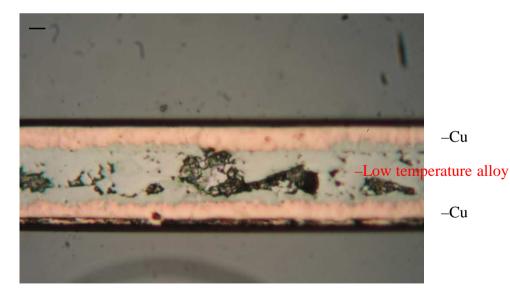

## .ow Temperature Interconnect

#### -Attatchment between devices with TSV s need low stress (low temp) bonding

-Low temperature SLID (Solid Liquid Interdiffusion)

New research based on multi element compounds to reduce melting point during bonding

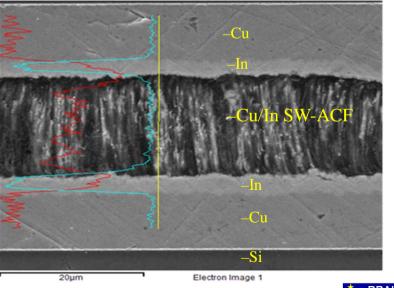

-SEM and EDX line-scan of Cu/In www.tyndatterface

-SW-ACF bonding on In/Cu pads

- •Peak bonding Temperature: 180 °C

- •Bonding time: 240 s

- •Bonding pressure: 2.2 N/mm<sup>2</sup>

- •Heat rate: 3 °C/s

- Shear testing showed a bond strength of ~7.2 kgf

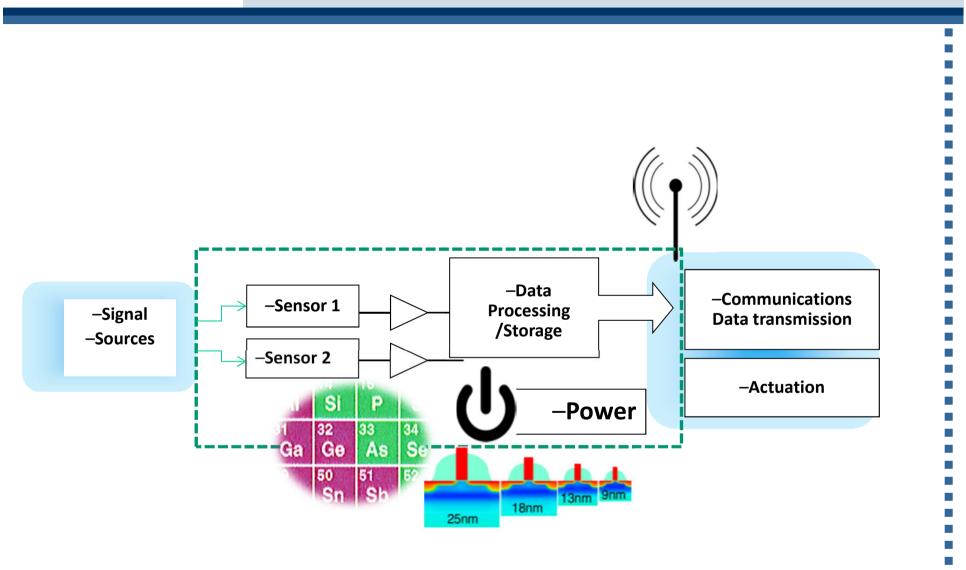

#### Much More Than Moore

# SMART Systems - Impacting Society and the Economy

www.tyndall.ie

## Conclusions