# Integrated power & energy efficiency

Power device technologies, simulations, assembly and circuit topographies enabling high energy efficiency applications

Catrene Scientific Committee Working Group: Integrated power & energy efficiency

## Integrated power & energy efficiency committee members

Prof. Gaudenzio Meneghesso (UniPD - IUNET) - Coordinator

#### Working group members:

Dr. Anton Bauer (Fraunhofer IISB) Prof. Braham Ferreira (TU DELFT) Dr. Jean-Pierre Ganne (Thales Research & Technology) Dr. Renaud Gillon (On-Semi) Thomas Harder (General Manager ECPE) Dr. Eckart Hoene (Fraunhofer IZM) Dr. Jürgen Lorenz (Fraunhofer IISB) Dr. Peter Moens (On-Semi - B) Prof. Mikael Östling (KTH) Dr. Jelena Popovic (TUDelft) Dr. Jan Sonsky (NXP - Belgium) Dr. Renaud Stevens (SOITEC) Dr. Steve Stoffels (IMEC)

#### Other contributors:

Dr. Oliver Ambacher (IAF) Dr. Jean-Jacques Aubert (CEA-Leti) Dr. Filip Bauwens (ONSemi) Dr. Marco Camalleri (STMicro) Dr. Wolfgang Dettmann (Infineon) Dr. Peter Friedrichs (Infineon) Dr. Klaus Heyers (Bosch GmbH) Dr. Richard Lebourgeois (Thales) Prof. Leo Lorenz (President ECPE) Dr. Angelo Magrì (ST Micro) Dr. Frans Pansier (NXP) Dr. Alfonso Patti (STMicro) Dr. Joachim Pelka (Fraunhofer VµE) Caroline Perfetti (Soitec)) Dr. Martin Rambach (Bosch) Daniel Rondi (Soitec) Dr. Matthias Rose (NXP) Dr. Phil Rutter (NXP) Dr. Lothar Schindele (Bosch GmbH) Yann Sinquin (Soitec) Dr. Daan van Wyk (UJ) Prof. Enrico Zanoni (University of Padova)

## Summary

| -  |                                                                              |    |

|----|------------------------------------------------------------------------------|----|

|    | tegrated power & energy efficiency committee members                         |    |

| 1. | Abstract                                                                     |    |

| 2. | Executive Summary                                                            |    |

| 3. | Section 1: Power electronics enabling energy efficiency                      |    |

|    | Energy Savings Potential                                                     |    |

|    | Energy supply and CO <sub>2</sub> emissions                                  | 11 |

|    | Role of power electronics in improving energy efficiency in key applications | 11 |

|    | Power electronics in the global view                                         | 13 |

|    | Conclusions                                                                  | 16 |

| 4. | Section 2: Power devices                                                     |    |

|    | Figure of merit and Benchmarking Power- Si – SiC – GaN                       |    |

|    | Electrical parameters                                                        |    |

|    | Power transistor figures of merit                                            | 20 |

|    | Benchmarking                                                                 | 21 |

|    | Conclusion                                                                   | 22 |

|    | Si –Power devices                                                            |    |

|    | Discrete vs. Integrated Power Devices                                        | 26 |

|    | Low Voltage MOSFETs                                                          |    |

|    | High Voltage MOSFETs                                                         | 31 |

|    | IGBTs                                                                        | 34 |

|    | Device vs. Application landscape                                             | 35 |

|    | Si-power Devices, key topics & requirements for future funded projects:      |    |

|    | SiC Power semiconductor devices                                              | 38 |

|    | Introduction                                                                 |    |

|    | High voltage blocking                                                        | 40 |

|    | SiC diodes/rectifiers                                                        | 40 |

|    | Switch devices                                                               | 40 |

|    | JFETs                                                                        | 41 |

|    | MOSFETs                                                                      | 41 |

|    | Bipolar Junction Transistors                                                 | 41 |

|    | Very High Voltage - High Injection Devices                                   | 42 |

|    | Concluding remarks and Issues of concerns for SiC power devices              |    |

|    | Power GaN Device Technology                                                  |    |

|    | GaN material and device physics                                              | 45 |

Catrene Scientific Committee Working Group: Integrated power & energy efficiency

| Device architectures                                                     | 47               |

|--------------------------------------------------------------------------|------------------|

| Ohmic contacts                                                           |                  |

| E-mode devices                                                           |                  |

| Breakdown voltage engineering and limitations                            |                  |

| Conclusion                                                               | 51               |

| New materials and Substrates for WBG power devices                       | 56               |

| State of the art of the existing substrates for power devices            | 56               |

| Supply Chain of GaN and SiC substrates                                   |                  |

| Large GaN-on-Si substrates                                               | 60               |

| Advanced substrates                                                      | 64               |

| Innovation through layer transfer technologies                           | 65               |

| Simulation of Power devices                                              |                  |

| Process Simulation                                                       | 68               |

| Device Simulation                                                        | 70               |

| Mixed-Mode simulations                                                   | 71               |

| Circuit Simulation                                                       | 72               |

| Conclusion                                                               | 73               |

| Reliability issues in Si-Power devices                                   |                  |

| Overview of Power MOSFET reliability and qualification testing           | 74               |

| Oxide Reliability Effects.                                               | 76               |

| Thermally Induced Degradation and Failure.                               | 79               |

| Interaction Mold Compound—Si Structure.                                  | 80               |

| Silicon Defects.                                                         |                  |

| Radiation Hardness                                                       |                  |

| Conclusion                                                               |                  |

| Reliability issues in SiC power devices                                  |                  |

| Intrinsic defects                                                        |                  |

| Gate oxide stability                                                     |                  |

| Contact and metallization stability                                      |                  |

| High temperature stability                                               | 92               |

| Reliability issues in GaN power devices                                  |                  |

| Parasitic and dispersion effects:                                        | 93               |

| Reliability issues                                                       |                  |

| High temperature performances, thermal management, Limits of H operation | ligh temperature |

| Wide bandgap devices                                                     |                  |

| High temperature packaging                                               |                  |

| High temperature Gate drives                                             |                  |

| $\sigma$ · · · · · · · · · · · · · · · · · · ·                           |                  |

| Passives for High Temperature Power Electronics                                         | 110          |

|-----------------------------------------------------------------------------------------|--------------|

| Packaging issues and solutions for Power devices                                        | 113          |

| New packaging technologies for high power modules                                       | 113          |

| High efficient double sided cooling technology (for E-Mobility)                         | 114          |

| Embedding                                                                               | 114          |

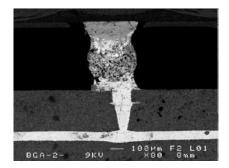

| Die attach                                                                              | 115          |

| Top side interconnects                                                                  | 115          |

| Encapsulation                                                                           | 115          |

| High power Passives for Inverter / Converter                                            | 116          |

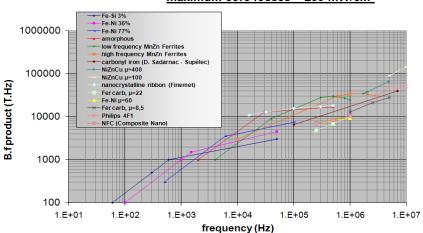

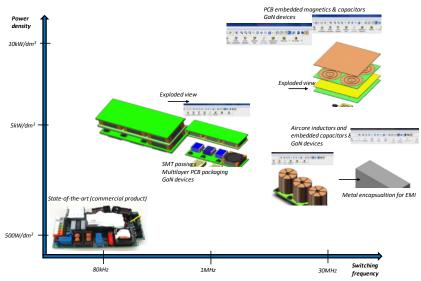

| Magnetic components and frequency evolution of SMPS (from kHz to multi MHz)             | 116          |

| Trends in the evolution of magnetic components                                          | 119          |

| Research directions on high frequency passive components: four challenges               | 120          |

| 5. Section 3: Integrated Power and Efficient conversion circuits                        | 122          |

| Integration of WB devices into systems and circuits                                     | 122          |

| Alternative approaches are needed to system design                                      | 123          |

| Capacitive effects and issues                                                           | 124          |

| Evolution of existing technology platforms                                              | 124          |

| Bridging the gap between power and RF electronics                                       |              |

| High temperature operation                                                              |              |

| Gate drivers (co-integration) (GaN)                                                     | 126          |

| GaN gate driver requirements                                                            | 126          |

| Monolithic integration approaches                                                       | 129          |

| Heterogenous integration                                                                | 131          |

| GaN drivers and GaN co-integration, key topics & requirements for future funded project | <b>s</b> 131 |

| Thermal design and thermal management                                                   | 132          |

| Spreading the heat of small WBG dies                                                    | 132          |

| Thermal management vs. high frequency operation                                         | 133          |

| New thermal management design approaches                                                | 133          |

| High temperature operation                                                              | 134          |

| Thermal management of passives                                                          | 134          |

| Market penetration                                                                      | 134          |

| EMC of power devices                                                                    | 135          |

### 1. Abstract

Today already 40% of the world wide used energy is provided by electric power. It is expected that this share is going to rise to about 60% by 2040. This enormous amount of energy not only needs to be produced environmentally friendly, but it also should be distributed and used efficiently. For that, power electronic devices, circuits, modules and systems are needed in large numbers, so that, depending on the application, the suitable electric current electric voltage and frequency profile can be produced. The goal is to consequently minimize the dissipation factor and the production costs of these devices. The introduction of efficient power electronics in the fields of renewable energies and automobile electronics, can, by itself, enable possible energy savings from 20 to 35%. Innovations span from new advanced semiconductor materials, like a promising class of novel wide bandgap semiconductors (WBS), to new device technologies (advanced Si, vertical and lateral structures, etc.) to innovative circuit and system solution able to optimize energy conversion, energy storage, energy distribution and finally energy usage.

European industry and academia are amongst the global leaders in the complex More Than Moore technologies for the power electronic devices and Europe is leading in measures towards reducing green house gas emissions. This perfect match of technological leadership and ambitious societal targets could be leveraged by European and national funding for power electronic devices and technologies. Collaborative projects will strengthen the European industrial and academic landscape by securing and generating employment in a key enabling technology domain enabling energy efficient solutions for the future.

The scope of this document is to present the state of the art of the available power devices, highlight the main potential and limitation and indicate the path for the future materials and device technology that will be required to meet the request for a green energy world. Starting with a general introduction on the role of power electronics in improving energy efficiency, a summary of the main advances in device technology will then been presented. Advanced new Si technologies, new power device based on Silicon Carbide (SiC) and Gallium Nitride (GaN) will be described in detail together with a benchmark of the different technologies, highlighting the main potential and limitation of the different technologies. Indeed, TCAD simulation tools will play a crucial role for the development of highly performing, robust and reliable power devices, and for this reason a section is dedicated also to this topic. The main challenges for the availability of new materials and new substrates will be discussed. These materials and substrates need to be available with very high quality and at very low cost. Then, reliability issues of the different power devices technologies (Si, SiC and GaN) will be presented. This study will highlight the main issues, which are limiting the production of reliable devices in applications where, next to efficiency, also reliability is a must (automotive, satellite, ...). Furthermore, passive devices and packaging will very likely present the main bottleneck for exploiting the full capabilities of future WBS devices, and will require the development of new concepts ; these aspects will be discussed in the two specific sessions. Finally, the main open issues for the integration of wide band gap semiconductors devices in in systems will also be discussed with specific attention to thermal management and electromagnetic interference and immunity.

This document is the result of the work of many European researchers either from industrial and academic research centers, that have decided to produce a document that hopefully will represent a starting point for those who would like to know about the development of power technologies for the implementation of very high efficient systems. To facilitate the reader, an executive summary reporting the main point collected in this document, is presented in the following pages.

## 2. Executive Summary

#### **Energy Savings Potential**

Power Electronics is the technology associated with the efficient conversion, control and conditioning of electric energy from the source to the load. It is the enabling technology for the generation, distribution and efficient use of electrical energy. It is a cross-functional technology covering the very high Giga Watt (GW) power (e.g. in energy transmission lines) down to the very low milliWatt (mW) power needed to operate a mobile phone. Many market segments such as domestic and office appliances, computer and communication, ventilation, air conditioning and lighting, factory automation and drives, traction, automotive and renewable energy, can potentially benefit from the application of power electronics technology. The ambitious goals of the European Union to reduce the energy consumption and  $CO_2$  emissions can only be achieved by an extensive application and use of Power Electronics, as power electronics is the basic prerequisite for:

- Efficiently feeding-in wind and solar energy to the grids;

- The stabilization of the power grids with increasing share of fluctuating renewable energies;

- Highly efficient variable speed motor drives;

- Energy efficient and low-emission mobility with hybrid and full electric vehicles;

- An energy saving lighting technology;

- Efficient recovery of braking energy;

- Energy management of batteries;

- Control appliances and building management systems via the grid interface (smart grids).

The estimated energy savings potential that can be achieved by introducing power electronics into systems is enormous, more than 25% of the current electricity consumption in the EU countries. Since power electronics is a key technology in achieving a sustainable energy society, the demand for power electronics solutions will show significant growth in the coming decades. The European industry holds a strong position in the field of power semiconductors and modules and is establishing a wide band-gap semiconductors technology base. Europe also has high quality power electronics research groups at universities and research institutes with well-established networks and associations in Europe to provide platforms for discussion, cooperation and joint research. On the other hand, outsourcing of research and technology to other countries (not only Japan, USA, but also emerging countries), strong research increment in these countries, and the possibility of key European companies being taken over by competitors from Asia, make it even more critical for Europe to keep up with the technological development. This requires continuous investments in research and development.

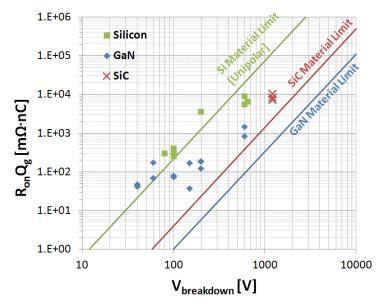

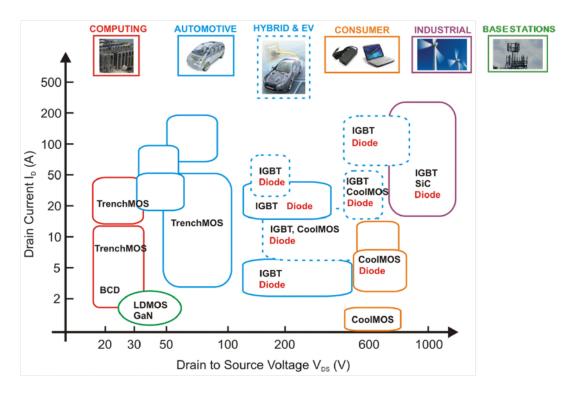

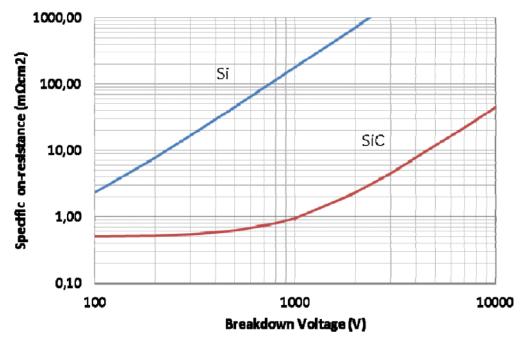

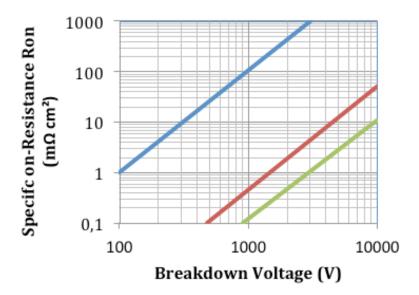

#### Benchmarking

In this section the most important figure of merit for switching power are reported for the latest generation of power components on the market, and this for different competing technologies. It is shown that the FOM for silicon technologies are close to material dictated limits and it will be hard and expensive to get further incremental improvements in performance. GaN and SiC on the other hand are disruptive technologies that offer orders of magnitude better FOM's than silicon. First generation products already show figures of merit, which are a factor 4 to 5 better than the latest generation of silicon technologies, with much headroom for future improvements. For GaN the biggest gain for the FOM is currently achieved in the medium voltage range (200V-600V), while for the low voltage range the contact resistance needs to come down further and currently puts a limit on the low voltage range (1200V), due to its high cost, which makes it difficult to compete in the lower voltage ranges. Investment in GaN should focus on optimizing it's advantage in the medium power range and driving the cost of the products down to compete more easily in this market. The medium voltage range houses market segment such as

home appliances and consumer electronics and thus present a huge potential market opportunity. At the same time effort should be spend on lowering the contact resistances in the GaN material to allow penetration of the technology in the lower voltage ranges, where there is a huge market for switched mode power supplies for IT and servers. SiC should leverage its strength at the high voltage ranges. Power transmission and large electrical engines such as locomotives should be a potential market and funding should focus on developing SiC technology to displace established IGBT's and Thyristors in this voltage range.

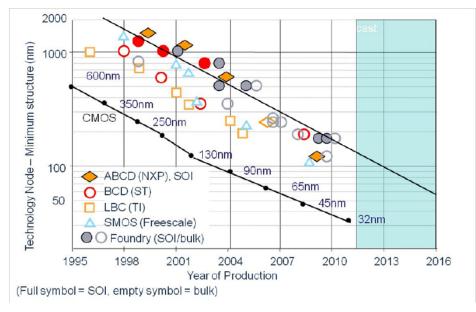

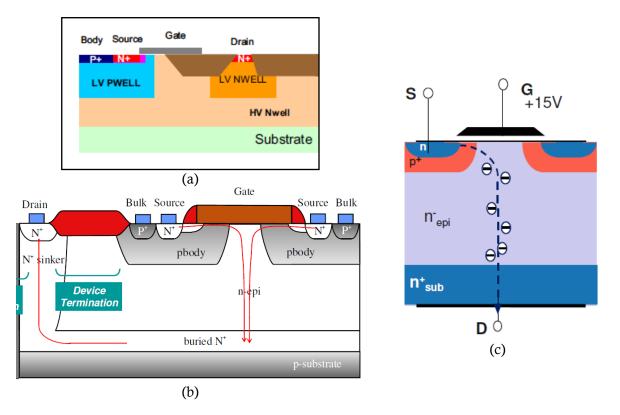

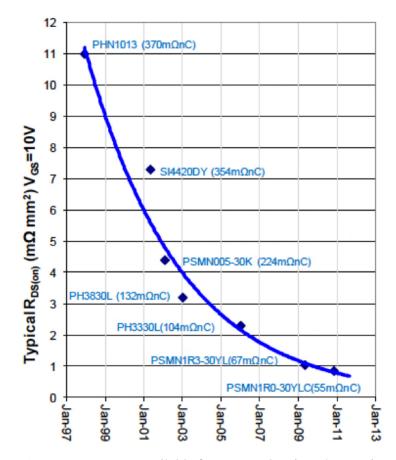

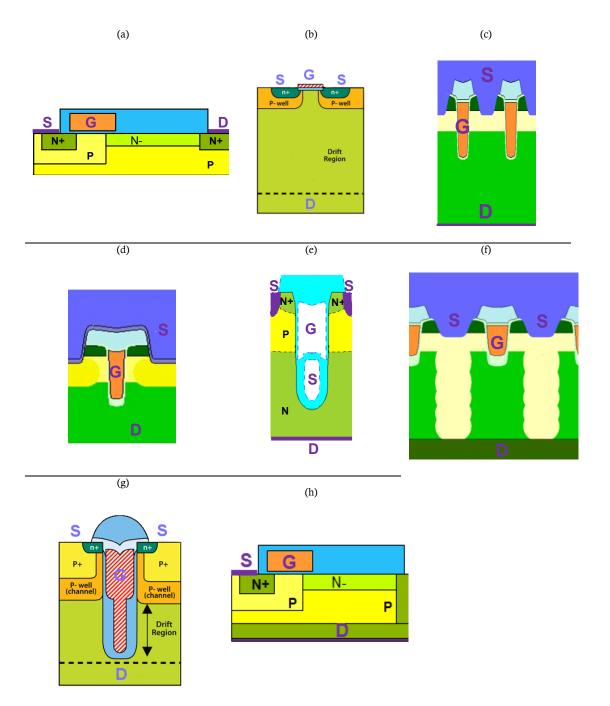

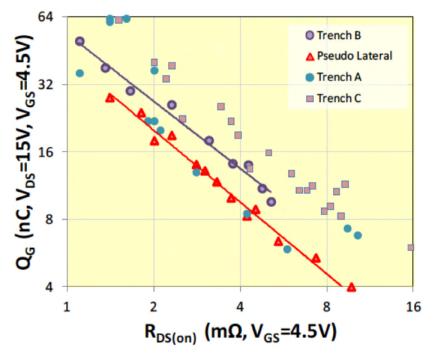

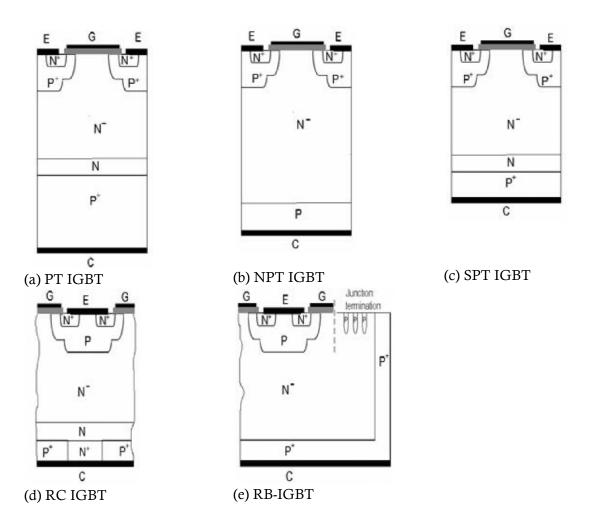

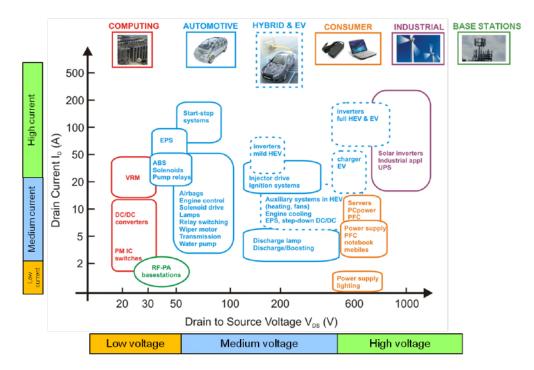

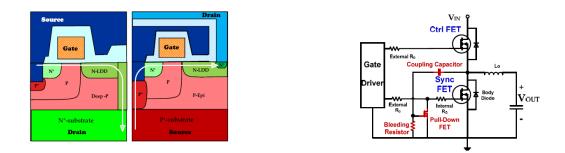

#### Si – Power devices

Si power devices have evolved over last several decades and dedicated device structures were engineered for different voltage classes. Along the way, numerous innovations have been realized to improve different aspects of device performance often beyond the so-called silicon-materiallimits. This chapter will start with discussion of key differences between discrete and integrated power devices and the following sub-sections will zoom-in to different available discrete technologies, including Low Voltage MOSFETs, High Voltage MOSFETs and IGBTs. Each section will cover key device types and innovation trends, including comparative performance assessment of the different competing components. Secondly the essential manufacturing technologies required to produce the different components will be discussed. Thirdly typical failure modes and reliability aspects specific to each technology type will be addressed. Finally fundamental performance limitations will be outlined. This will provide a good link to the other parts of the report discussing potential of wideband-gap based power components. As the device scaling continues, higher switching frequency is utilized and operating temperature increases, one of the innovation trends is towards so-called "smart discrete". These are components with on-chip integrated self-protection components. This part of the report will conclude with mapping the different power components and technologies on applications and circuit topologies.

#### SiC Power semiconductor devices

This subsection will focus on the state of the art in silicon carbide power device technology. A general overview will be presented on the status of silicon carbide wafer quality and availability. A brief discussion on possible switching speed advantage by using SiC devices vs traditional Si devices will be included. Size and weight advantages will be demonstrated. The second part will focus on current and future MOSFET devices. Fabrication strategies as well as a discussion on fundamental and practical performance limitations are included. A special focus will be on oxide properties and hence channel mobility. The third part is devoted to JFET devices and fabrication strategies. Current device ratings and availability as well as high temperature properties. The fourth part concerns bipolar junction transistors. Also here current fabrication strategies and device designs will be explored. A paragraph will also be devoted to operation under harsh environments. High voltage design above 3 kV will be included as well as high voltage junction termination extension structures.

#### Power GaN Device Technology

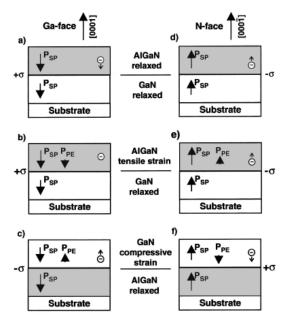

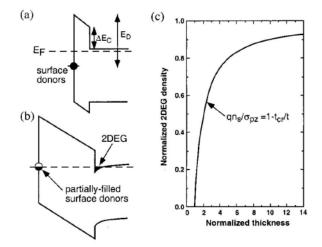

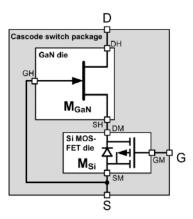

The research and development of GaN technology for power switching has made large strides in the past decade, several key challenges have been addresses since the inception of GaN as a power technology. To succeed as a power technology, the transistors need to exhibit a high breakdown voltage, a low on-resistance, a low leakage current a positive threshold voltage, high stability, reliability and should be cost competitive (at least at system level) with established silicon technologies. It has been shown by several research labs, universities and companies that GaN components do exhibit figures of merit which are an order of magnitude better than what is achievable with silicon and even SiC. However several key issues remain. Beyond the obvious challenge of scaling the technology to higher breakdown voltages and power levels, there were some other less obvious challenges. Historically GaN HEMT's were grown on a SiC substrate. The high price of this solution would make it difficult for GaN to compete in the world of power

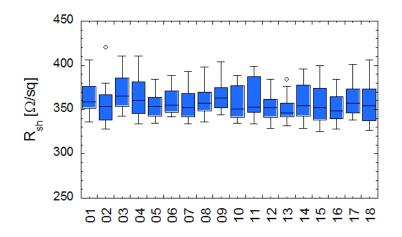

electronics. To address this issue, researchers have introduced the GaN-on-Si technology which removed the expensive SiC substrate and leveraged the industrial strength of the large install base of silicon fabs. To ensure CMOS compatibility, necessary for processing in a silicon fab, all Au containing steps had to be removed from the process. This has meant a re-optimization of the ohmic contacts with silicon compatible metals. To secure the leadership of Europe in GaN technology, we need to make sure that we leverage the strength and cost competiveness of the GaN-on-Si technology and make targeted investments to bring this technology further along in its maturity level. An important step in reducing the overall costs of production is scaling up the wafer size to 200mm. First demonstrators have been shown on 200mm wafers, but further optimization is needed to increase yield, assess reliability and evaluate proper packaging techniques for these components. Furthermore, the ohmic metal stack and gate metal stack should be re-optimized to ensure silicon compatibility, while at the same time showing reproducibility, stability and a good performance. Contact resistance and gate leakage are key metrics for this optimization. Also, functional demonstrators for target applications would make a strong case for field testing the technology and identifying key issues in early stage of development. Currently the only GaN devices on the market (EPC) have a maximum breakdown voltage of 200V. To capture larger portions of the market and assure market leading performance in 90% of the power market, it would be necessary to scale up the technology to at least 600V. Demonstrates in literature have shown breakdown voltages of 2000V, with record RonQg products, an order of magnitude below silicon. However, none of these technologies have been proven outside of research labs, and use tricks that might not be suited for large scale fabrication. Moreover, reliability and high voltage dispersion data has not been presented for these components and should all be addressed before high voltage GaN components can be introduced in the market. If Europe wants to play a leading role in this market, these issues should be addressed. A final challenge for GaN devices, which would require dedicated research and investment is in achieving true enhancement-mode (e-mode, normally off) operation. GaN devices are naturally depletion mode (d-mode), which means that in the case of a gate driver failure, the device will conduct current, potentially destroying the entire system. This mode of operation is not preferred by system designers, who prefer e-mode. Currently manufacturers prefer to couple a well-developed d-mode device with a low voltage silicon component in series. However, a high performance e-mode device would be the preferred solution from cost and performance perspective. If Europe wants to play a role in the future of GaN, resources should be spent on achieving reliable GaN transistors, with low on-state resistance and true e-mode operation. Several companies in US and Asia are heavily investigating these devices; therefore Europe cannot afford to miss the train.

#### New materials and Substrates for WBG power devices

As the electrical power supply demand is increasing with the generalization of electric devices in the consumer market, the challenge of the power management is to provide highly efficient components that reduce the power loss in all conversion steps needed in between electrical power generation, electrical transportation and final power use. To answer the technical challenges for high efficiency and small form factor, wide band gap material are gaining strong interest, in particular Gallium Nitride material (GaN) that enables performance breakthrough in key parameter devices compared to the established Si based devices. A number of challenges are however associated with the development of efficient GaN substrates, the first being a limited offer for industrial epitaxial GaN wafers in Europe at the moment. On top of this, there are currently no substrates at market compatible price for the next generation device with high performances, which will require a better material quality. This limits the innovation of European industrial power devices makers. Finally, typical key players in automotive or energy conversion are expecting the emergence of reliable GaN substrate providers to secure the global supply chain and allow the development of new innovative and competitive devices. New advanced substrates based on customized thin film stacking technologies could give access to high performance, flexible and thick GaN and overcome the challenges of directivity and dislocations due to lattice matching and

thermal expansion variation. In this chapter WBG material and substrates for power devices will be described, focusing more specifically on the 2 most widely used, SiC and GaN. In the first section, the various existing technologies will be reviewed and assessed, and the inherent properties of materials such as SiC and GaN will be discussed. The key aspect of the supply chain for SiC and GaN will be evaluated in the second section. The third section will focus on the large GaN on Silicon substrates. Finally, we will discuss the emergence of a new type of advanced substrates.

#### Simulation of Power devices

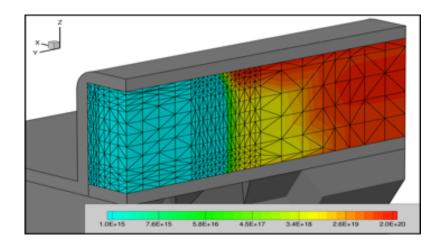

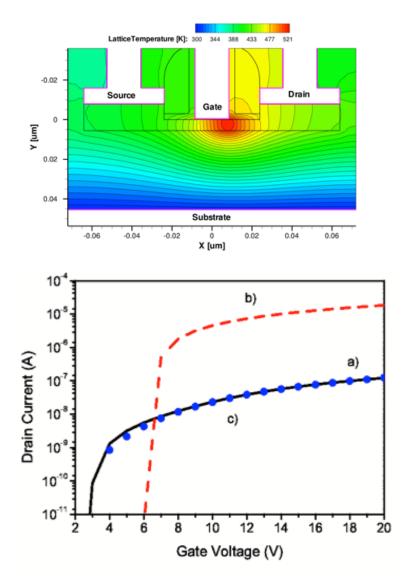

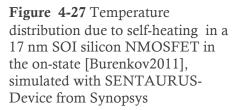

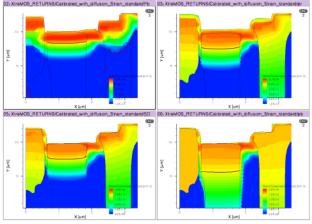

It is common understanding in industry and research that TCAD simulations are an invaluable mean to investigate and optimize new processes and devices and to identify and analyze factors that cause parametric yield loss in manufacturing, when new processes, new device architectures and/or new materials are introduced. Appropriate use of TCAD strongly contributes to the reduction of development times and costs, and to increasing product yield on a wide range of technologies. This very well justifies investment in the development of the models and tools needed to carry out the required simulation studies. Especially, new, extended or adapted physical models must be developed and be made available in the standard tools used in industry, in order to cope with the requirements of specific materials, processes and architectures used for power devices. Technology Computer Aided Design (TCAD) has during the last decades developed into a key tool to support the development and optimization of semiconductor technologies, devices and circuits. Its scope extends from the simulation of process equipment through simulation of processes and devices to the simulation of circuits and systems. It is based on a thorough understanding of the physical effects involved at all these levels, the extraction of the required physical parameters, and the implementation of the models developed into simulation tools which enable an efficient and predictive simulation. The International Technology Roadmap for Semiconductors ITRS among others also contains a chapter on Modeling and Simulation. This chapter gives an estimate of about one third for the reduction of development times and costs for best practice cases in nanoelectronics. This should also be the aim for power electronics. Because the core of simulation comprises quantitative physical understanding and efficient algorithms, leading-edge simulation tools are mostly quite generic and may be used for a large variety of processes and devices. The range of such applications spans from aggressively scaled memory and logic devices to RF and power devices. In this chapter, the main additional features needed for the simulation of power devices and their fabrication, as well as the state-of-the art in these areas, are summarized. Important additional requirements are identified in the areas of process, device and circuit simulation. As part of this, also the numerical algorithms are faced with additional challenges.

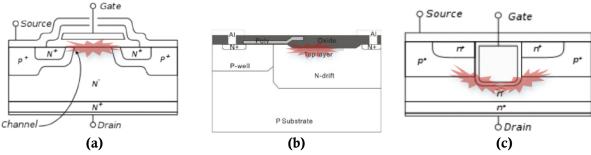

#### **Reliability issues in Si-Power devices**

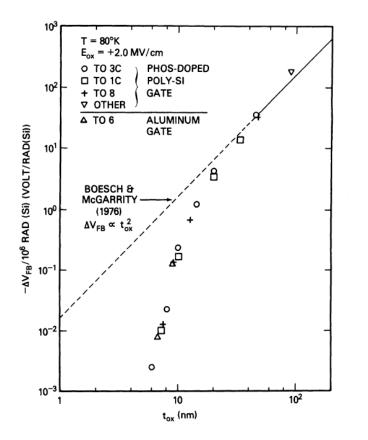

Today Si power devices and technologies are in the market for a very long time, and have matured in terms of reliability and qualification level. Due to the very high quality of Si starting material, and the thermally, chemically and electrically stable  $SiO_2$  with low interface states, Si power device technologies are qualified for the most demanding markets, like e.g. automotive applications, achieving very low ppm levels. However, since Si power devices have to compete against wide bandgap devices based on SiC and GaN, both having superior material parameters, novel and more advanced structures and features have to be implemented to remain costcompetitive, e.g. trench gate structures, deep trench super-junction structures, thin wafer technology etc. These new features introduce new reliability challenges to be worked on and to improve: high quality gate oxides grown on trench sidewalls, and the subsequent acceleration testing and modeling; void free epitaxial growth in deep trench structures; strain management in thin Si fins. This section provides an overview of the most relevant reliability issues in Si based power devices (diodes, MOSFETs, IGBTs,...). Although Si technologies are well established and have proven long term reliability, some important reliability issues deserve further study and improvement, especially for high voltage devices. As many silicon-based power devices are MOStype (power MOSFETs, IGBTs etc), and as power MOS devices have a large Si area (several mm<sup>2</sup>

up to a few cm<sup>2</sup>), both intrinsic as well as extrinsic reliability of the dielectric is important. The former is especially true for high temperature operation, since power MOSFETs can reach high local junction temperatures, leading to an accelerated dielectric degradation. The latter is defect driven, and scales with the device area. On top, many novel Power MOSFETs and IGBTs have trench gates or trench super-junctions, so that oxide and interface quality on trench sidewalls is important. To account for the need of higher voltages in the Si-Power devices, very often as in the case of IGBTs and diodes, the Silicon background doping is severely lowered. This puts more constraints on the power limitations since a low current density in the device during switching can already destroy its avalanche ruggedness. This effect is well understood and some tricks exist to overcome the problem, e.g. introduction of buffer layers, injection of minority carriers, etc. However this always comes at a cost and thus avoiding the sensitivity towards destruction by low current density switching is favored. Materials with higher maximum electric field capability compared to Silicon are preferred in that respect. Additional reliability issues mainly include passivation integrity failures, due to the lack of sufficient screening of the mobile charges in the mold compound from the lowly doped epi layers in the device termination (HTRB and H3TRB testing), cracking of the passivation layers, and device parameters shifting upon avalanche conditions (repetitive UIS testing)

#### Reliability issues in SiC power devices

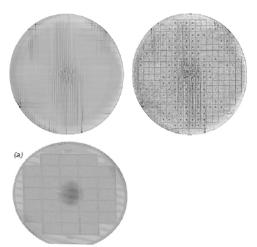

Despite the fact, that power devices on 4H-SiC shows superior properties compared to silicon due to its wider band gap, and that several devices, like Schottky-barrier-diodes, JFETs, MOSFETs etc., are already on the market for some time, the penetration of the power device market by SiC devices is not as strong as it should be. SiC power devices target next to others at uninterrupted power supplies, automotive, wind turbine, PV inverters or grid applications. Here the users of power devices for the power electronic systems are very conservative. Their main concern is next to the price, the reliability of the devices. Except the SB-diode, which is sold times without numbers, the other devices show no significant application in systems in the field so far and, therefore no thorough reliability data are available. This section will describe the reliability issues of 4H-SiC power devices. It is divided in four subsections. The first subsection will identify and describe defects in the 4H-SiC substrate and how they can propagate into the epitaxy layers or better how they can be reduced or even avoided by epitaxy. Here, also life-time enhancement in the bulk of the epi-layer will be considered. Key points are very high temperature sacrificial oxidation or carbon implantation with subsequent high temperature annealing to increase lifetime. Both, the appropriate epitaxy as well as additional carbon introduction can increase the minority carrier lifetime in pin-diodes significantly. The second subsection covers the stability of gate oxides in MOSFETs, but also, because the issues are comparable, the stability of oxide passivation in high power applications. Here, interface state densities and their influence on threshold voltage and on channel mobility is the biggest reliability issue in 4H-SiC power devices in and of itself. Furthermore, the build-up of charges in the oxide and the dielectric breakdown fields will be addressed. In the third subsection the reliability of Ohmic- as well as Schottky-contacts will be considered. If the interface between metallization and SiC is not perfectly smooth or the consistency of the used metal layers is not well controlled, phase separation or even precipitation in the contact metallization will occur which will negatively influence the device stability. In the last section the thermal stability will be addressed very briefly. Finally the following aspects will be covered: i) high temperature stability ii) reliability iii) availability of high temperature applicable packaging and assembly and iv) passives for high temperature.

#### Reliability issues in GaN power devices

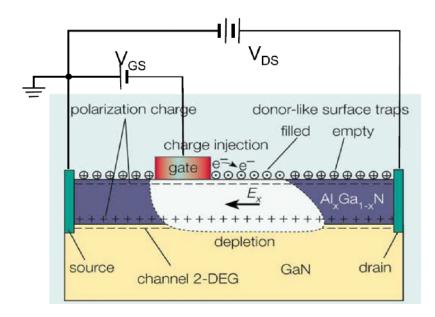

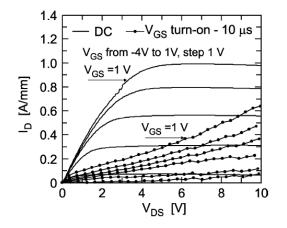

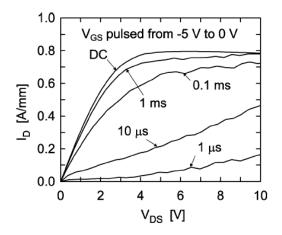

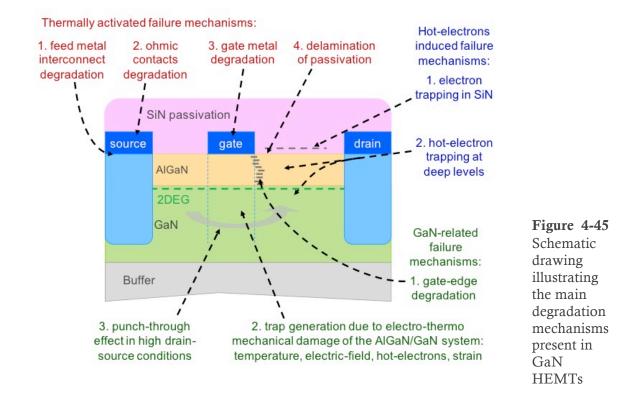

GaN High Electron Mobility Transistors are excellent devices for high power and high frequency applications. Thanks to the advantageous material properties of GaN-based semiconductors, such devices will operate at very high drain voltages, where the extremely high electric fields drive high current densities in the two-dimensional channel electron gas at fairly high channel temperatures. The resulting operating conditions are by far more severe than those

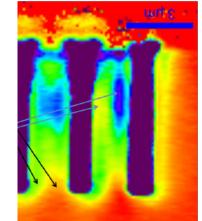

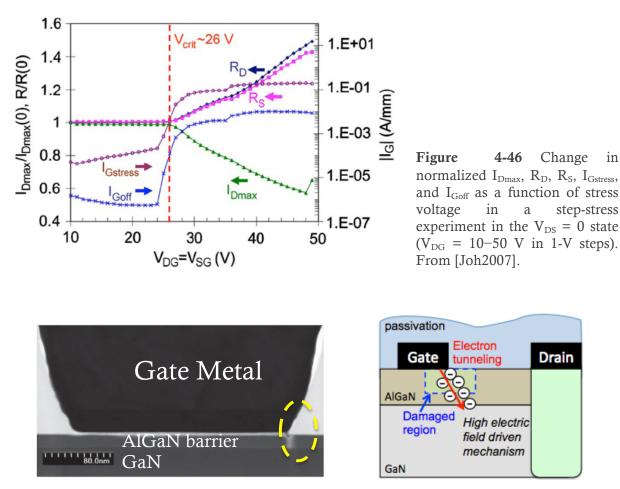

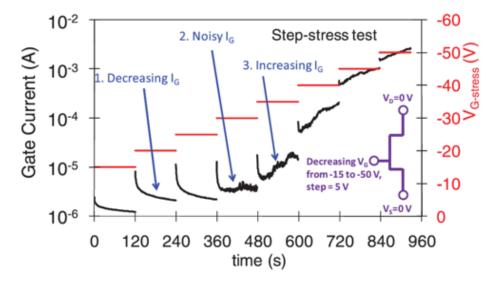

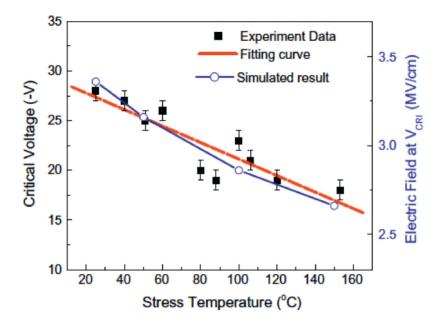

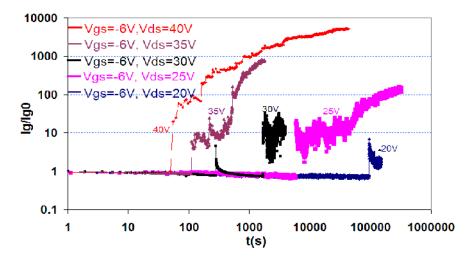

encountered by any other semiconductor developed so far. Even though significant improvements in the quality of GaN-related substrates and epitaxial structures have been achieved in the past few years, GaN based devices still have material-related issues which need to be resolved. This section will present an overview of the parasitic and reliability issues in Gallium Nitride-based transistors. From the parasitic point of view the following represent the main open issues related to the GaN-HEMTs technology: (i) trap-related effects leading to the deleterious dynamic R<sub>DSON</sub> (due to surface, interface, bulk traps), (ii) gate leakage current, (iii) kink phenomena. The effects of surface, interface and bulk traps will be discussed, on the basis of experimental data obtained by means of pulsed measurements, Deep Level Transient Spectroscopy, photocurrent spectroscopy and of 2D device simulation results. Reliability issues in GaN HEMTs devices will be also largely described. The main target of this section is to highlight the peculiarity of the degradation mechanism in these devices. In particular, it will be shown that new failure mechanisms are present in the devices based on this material system (gate edge degradation and semiconductor cracking), and also that many of the observed degradation mechanisms do not completely follow the typical activation energy law, that have been (and is nowadays) largely applied in Silicon power devices. Failure modes and mechanisms of GaN HEMTs will be critically reviewed, including the time-dependent gate leakage increase during reverse bias tests, hot-electron-induced drain current degradation, gate and ohmic contact degradation, delamination of passivation and electron trapping. Finally, a review of the most commonly known technological countermeasures for alleviating reliability issues will also be briefly described (Single and multiple field plate designs, Cap layer (thin GaN cap, p-type GaN cap, buffer optimization (heterostructure, Fe-doping etc), passivation (in-situ, exsitu), MISHEMT structure versus Schottky-based HEMT etc.

#### High temperature performances, thermal management, high temperature operation

Increasing the working temperature of power devices and modules is a key issue for improving and simplifying the heat exchangers and cooling systems of power applications as well as for introducing power devices in high temperature environments such as deep drilling or aeronautics. New technologies around wide bandgap semiconductors, silicon carbide and gallium nitride mainly, are important breakthroughs to improve on the intrinsic temperature limitations of silicon technology. But, while the new materials themselves are able to stand very high operation temperatures, thermal limitations may still occur at the device level, the module level or the system level. At the device level, the diffusion processes can reduce the lifetime but the main issue will certainly appear at the metallization level, increasing electromigration and requiring a shift from aluminum to copper. At the module level, increasing the working temperature will require the removal of insulating gels and a change in the nature of the packaging polymers. Thermal management will be the key. At the system level, increasing working frequency and temperature at the same time as well as the need for compactness will need to put the gate drives as close as possible to the devices, demanding the use of high temperature silicon logic technologies. And finally, one of the main temperature limitations can come from the passive components, essentially capacitors and their dielectric materials. Carefull attention has to be paid to this particular point.

#### Packaging issues and solutions for Power devices

The evolution of power semiconductors has arrived at a level where packaging restricts the achievable performance of the final device. A package for a power semiconductor has to remove the heat, provide security insulation against the heat sink, conduct current and has to be electromagnetically and thermo mechanically reliable. The development of solutions for these multiple requirements has to be based on in depth knowledge of application demands as well as material and production. This complexity is one reason, why European companies still have a leading position in the world market. The future development of packages has to face several aspects: (1) The increase of power density requires more sophisticated thermal design; (2) The possibility for higher junction temperatures can only partly be used due to the reduced live time of the package. A higher temperature would reduce system volume due to smaller heat sinks. This is especially valid for semiconductors with wide band gap like SiC an GaN; (3) More functions

included in the power semiconductor package can reduce system costs; (4) Higher switching slopes force a more precise electro-magnetic design of the package and will influence the technology selection; (5) Packaging technologies with longer life time pay off by reduced system costs; (6) Production processes always remain an issue for improvements. In this chapter these aspects will be worked out in detail with examples for applications.

#### High power Passives for Inverter / Converter

Magnetic components (inductors and transformers) are the limiting factor for the miniaturization of Switched-Mode Power Supplies. Increasing their switching frequencies enables the miniaturization of magnetic components, but materials properties and component designs vary with frequency. Wide bandgap semi-conductors components open the way to Multi MHz switching, but the materials and designs used for passive components in present high frequency (several 100 kHz) SMPS cannot be transposed. New materials and new designs must be developed for Multi MHz passive components. The following chapter is divided into three parts. In the first part we explain why high-frequency switching enables to miniaturize the passives, and how the choice of magnetic materials is closely linked with the switching frequency. We introduce a merit factor for power magnetic materials that characterizes their ability to transmit a high volumetric density of power with low power dissipation. We show how the preferred choice of magnetic materials, based on this criteria, depends on switching frequencies. In the second part we identify three current trends in the evolution of magnetic components: the development of new materials, the replacement of bulky components with planar shapes, and the research of technologies able to integrate the conductors with the magnetic materials inside a monolithic ceramic component, made by a multilayer ceramic technology. Although multilayer ceramic capacitors, chip inductors, and multilayer ceramic substrates have long been fabricated in this way, integrating different ceramic materials with metallic conductors in order to make multilayer integrated passive components is still a big challenge. To date only partial integration has been demonstrated, for instance of high-k materials for capacitors inside low-k ceramic substrates. In the third and last part four challenges are identified for the future research: High frequency, high power magnetic materials, Low thermal resistance and low dissipation, Components and windings at very high frequency, Capacitors and integrated passive components.

#### Integration of wide bandgap devices into systems and circuits

Wide bandgap (WB) materials offer the possibility to increase the switching speed and the voltage rating by an order of magnitude, compared to silicon. For this reason WB devices already show great potential as a replacement technology of Si in existing converter circuits and systems. However, in order to exploit the true potential that the new devices have to offer it is necessary to revisit the design of switchmode based circuits and systems. Point-of-load dc power supplies are leading the way in high switching frequencies. These power supplies operate at low voltages. With WB devices similar switching speeds are possible at line voltages so that power conversion of line converters should be possible at switching frequencies above 1MHz. Due to the very good voltage blocking properties of WB devices, resonant circuit topologies that were not favored by Si can become attractive when WB devices are used. High step up ratios of dc converters can in theory be achieved at high efficiency, which is important in applications such as photovoltaics. Industry favors 1.5kV Si IGT's to 2kV+ devices because the high voltage devices are much slower having too high switching losses. Field effect WB transistors can easily achieve high breakdown voltages at very high switching speeds. If the voltage is scaled then the energy stored in capacitive parasitic become more dominant and when combined with the fast dv/dt of WB devices a new problem is created. New circuit topologies and alternative resonant transition solutions are needed. WB devices could drive a disruptive change in power electronics technology if it becomes possible to do switchmode conversion in the 10 - 100MHz frequency range. This would yield unprecedented power densities and remove the need for filters for conducted EMI. However, to achieve this new electromagnetic design approaches need to be developed that are based on RF and microstrip theory. WB band gap devices can operate at higher temperatures than their Si counterparts which

useful for conversion systems that have to operate under extreme conditions. To fulfill the high temperature requirements not only the active switching devices need to withstand the elevated temperatures, but also the other components in the systems, passive components and sensors. Due to the limited availability of high temperature electromagnetic materials and consequently the smaller values of realizable inductors and capacitors and a smaller selection of sensors, it becomes necessary to find new circuit and topology solutions.

#### Gate drivers (co-integration) (GaN)

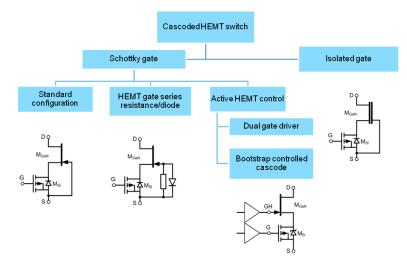

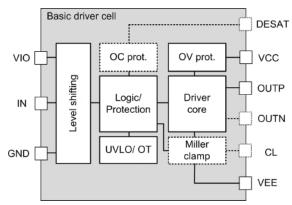

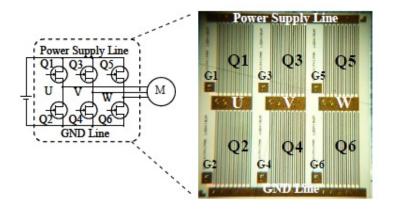

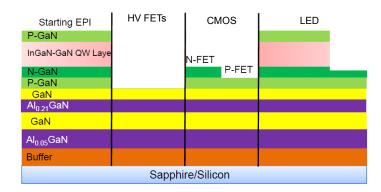

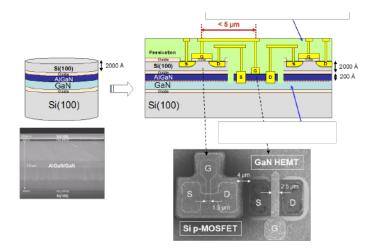

The GaN-on-Si technology and components are lateral and thus has a potential to integrate multiple components or even full circuitry together with the power devices. The ultimate dream is to co-integrate drivers with the GaN power components on the same chip. This ambition is motivated by removing parasitic stray inductances and other parasitics, which is required to operate the power supplies at multi-MHz or even at multi-10s MHz frequencies. This section will discuss first differences in gate-driver requirements for Cascoded-GaN components vs. enhancement mode GaN devices. Secondly different approaches being investigated by academia for monolithic integration of driver circuitry with GaN power devices will be outlined. Examples are building logic circuitry directly in GaN by means of advanced epitaxy and local removal of the selected layers to allow optimized islands for logic N-type transistor and logic P-type transistor. Other approach is based on building logic circuitry in the Si-carrier wafer and perform wafer bonding with GaN-layers. Finally, heterogenous integration approaches using multiple dies in a single package will be discussed and advantages and limitations of each approach will be sketched.

#### Thermal design and thermal management

The implementation of WBG devices in power electronic converters requires new thermal management approaches if the device is to be optimally exploited at high switching frequencies. For the same power rating the cross sectional area of the dies is substantially reduced. To remove the same amount of losses more and better heat spreading is needed. Furthermore, the devices are able to operate at higher temperatures so that larger thermal resistances could be tolerated. There is a trade-off between a high frequency operation and good thermal management in WBG converter. For fast switching the components have to be placed close to each other to minimize parasitic reducing the area for heat spreading. The capacitive coupling between the heat spreaders and heat sink impairs a high frequency operation. The packages suitable for high frequency operation require surface mount assembly and are unsuitable for large volume consumer applications. Furthermore, there is a change in the power loss distribution between active and passive components in WBG power converters. Power semiconductors are not necessarily the largest contributors to the total losses in WBG converters especially at very high switching frequencies. High frequency operation leads to miniaturization of electrically active parts of the converter, especially passives. The volume of thermal management parts, however, could take up a significant portion of the total volume.

#### How to strengthen the technological leadership and enhance employment in Europe

The European achievements in complex technologies, integration technologies and system solution are based on excellence of knowledge and on investments in the past, which are the base for future success. New investments in manufacturing technologies in Europe by leading industrial players (300mm wafer based power semiconductors, fab conversion to power technologies, module manufacturing, new equipment for wide band semiconductors) demonstrate the trust in own capabilities and in the future of keeping and enhancing the market shares. Further European collaborative projects will support the success path of Europe in power semiconductors.

## 3. Section 1: Power electronics enabling energy efficiency

### **Energy Savings Potential**

#### Thomas Harder (General Manager ECPE)

With the contribution of:

Jelena Popovic-Gerber (TU Delft)

#### Abstract

Power Electronics is the technology associated with the efficient conversion, control and conditioning of electric energy from the source to the load. It is the enabling technology for the generation, distribution and efficient use of electrical energy. It is a cross-functional technology covering the very high Giga Watt (GW) power (e.g. in energy transmission lines) down to the very low milli Watt (mW) power needed to operate a mobile phone. Many market segments such as domestic and office appliances, computer and communication, ventilation, air conditioning and lighting, factory automation and drives, traction, automotive and renewable energy, can potentially benefit from the application of power electronics technology.

The ambitious goals of the European Union to reduce the energy consumption and  $CO_2$  emissions can only be achieved by an extensive application and use of Power Electronics, as power electronics is the basic prerequisite for:

- Efficiently feeding-in wind and solar energy to the grids,

- The stabilisation of the power grids with increasing share of fluctuating renewable energies,

- Highly efficient variable speed motor drives,

- Energy efficient and low-emission mobility with hybrid and full electric vehicles,

- An energy saving lighting technology,

- Efficient recovery of braking energy,

- Energy management of batteries,

- Control appliances and building management systems via the grid interface (smart grids)

The estimated energy savings potential that can be achieved by introducing power electronics into systems is enormous, more than 25% of the current EU-25 electricity consumption [E4U2009, Popovic2012].

Since power electronics is a key technology in achieving a sustainable energy society, the demand for power electronics solutions will show significant growth in the coming decades. The European industry holds a strong position in the field of power semiconductors and modules and is establishing a wide band-gap semiconductors technology base. Europe also has high quality power electronics research groups at universities and research institutes with well-established networks and associations in Europe to provide platforms for discussion, cooperation and joint research. On the other hand, outsourcing of research and technology to other country (not only Japan, USA, but also emerging countries), strong research increment in these countries, and the possibility of key European companies being taken over by competitors from Asia, make it even more critical for Europe to keep up with the technological development. This requires continuous investments in research and development.

#### Energy supply and CO<sub>2</sub> emissions

The ever-increasing demand for energy, the shortage of fossil fuels and the need for carbon footprint reduction have resulted in a global awareness of the importance of energy savings and energy efficiency. This topic is taking high priority in today's society, leading to many governmental policies and measures, industrial programs and research, both in Europe and worldwide. Combating the energy and climate problem requires a complex, interdisciplinary approach involving technological solutions such as sustainable energy sources and more efficient energy use as well as political measures and general public commitment. In its Action Plan for Energy Efficiency, the European Commission presented an energy policy, which seeks to enable the European Union to reduce greenhouse gases by at least 20%, to reduce energy consumption by 20% and increase to 20% the share of renewable energies in energy generation by 2020. Furthermore, the European Union committed itself in 2009 to the reduction of its Greenhouse gas (GHG) emissions by between 80% and 95% by 2050. However, the interpretation of the energy savings target in EU law is much weaker than for the other two pillars of the EU climate package: greenhouse gases (GHG) and renewable energy. As a result, recent evidence suggests that the energy savings target will be missed by a wide margin even though it could be met largely through cost-effective measures. It should be noted that energy savings have the potential to cover half of the EU 80% emission reduction target for 2050.

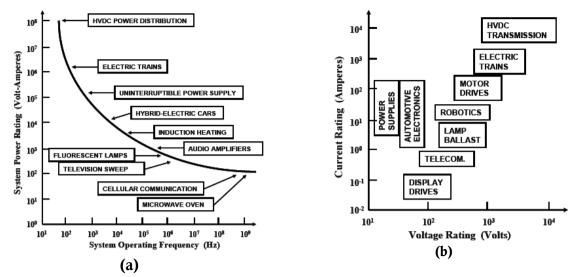

## Role of power electronics in improving energy efficiency in key applications

The demand for electricity is continuously growing and will continue to do so at a much faster rate than other energy sources over the coming decades, twice that of the overall energy consumption. Today 20% of final energy consumption in EU is electrical energy (which translates into up 40% of total primary energy), but this is predicted to grow significantly in the next few decades. Power Electronics is the technology associated with the efficient conversion, control and conditioning of electric energy from the source to the load. It is the enabling technology for the generation, distribution and efficient use of electrical energy. It is a cross-functional technology covering the very high GigaWatt power e.g. in energy transmission lines down to the very low milliWatt power needed to operate a mobile phone. Many market segments such as domestic and office appliances, heating, ventilation and air conditioning, lighting, computers and communication, factory automation and drives, traction, automotive and renewable energy can potentially benefit from the application of power electronics technology.

*Table 3-1* shows the large electrical energy consuming sectors that have significant energy-savings potential. A few major areas can be identified:

- Motor control It is estimated that motor-driven systems account for more than 50% of total electricity consumption (65% of industrial electricity, 38% of tertiary and 35% of residential). The energy-saving potential of Variable Speed Drives (VSDs) comes from the ability to control the motor speed to match the output with the system needs at very high efficiencies. The energy savings potential by introducing VSDs is estimated to be 30 40% for most applications. The technical potential for energy savings is for about 40 50% of all motors depending on the application, and given that VSDs have already been applied to about 15 20% of all motors the remaining potential is estimated to be about 30%. Combining all these figures, the total electrical energy-savings potential of VSDs is about 5 6% of the current electrical energy consumption.

- Buildings (commercial, industrial and residential)

- Lighting Currently 21% of total electrical energy is consumed by lighting. Savings of up to 70% of this can be achieved using technology solutions which are already on the market, such as replacing traditional fluorescent sources by high-efficiency ones using electronic ballasts (> 90% efficiency), and intelligent dimming based on

data for occupancy and daylight (collected by wireless sensors). This translates into 14% of the total electricity consumption. The savings will be greater with new technologies based on solid-state lighting (i.e. LEDs).

• Heating, ventilation and air conditioning (HVAC) – HVAC accounts for 40% of the total energy consumption in buildings (including electrical and non-electrical heating). Using advance control together with energy-efficient appliances it is possible to save around 20% of total energy consumption (electrical and non-electrical).

#### • Information and Communication Technology (ICT )

- Electrical energy demanded by *data centers and servers* in the Western Europe was 56 TWh in 2007 and is forecast to increase incrementally to 104 TWh in 2020. In a typical data center, less than half of this power is delivered to the compute load, which includes microprocessors, memory and disk drives. The rest of the power is lost in power conversion, distribution, and cooling. The use of advanced power electronics techniques, like new DC distribution networks, can lead to a 10% reduction of the required energy. The integration of ICT technologies and power electronics and improving energy management can save an additional 20%, and the implementation of best practices can lead to a 50% reduction, which translates into 1% savings of the total electricity consumption. Further research on reliability, implementation and cost reduction can further improve these numbers.

- Estimates indicate that the telecom industry consumes 1% of the global electricity consumption, and more than 90% is consumed by networks operators. Almost 30% of electrical energy savings can be achieved in *radio base stations* (RBS) by employing efficient power electronics technologies such as efficient power amplifiers and techniques for low consumption in standby mode.

- The annual electricity consumption related to standby functionalities and off-mode losses in the EU was estimated to have been 47 TWh in 2005. It has been estimated that the total annual energy savings potential for standby consumption in the EU is 35TWh, and power semiconductor manufacturers claim that more than 90% standby consumption reduction is feasible.

To summarize: the estimated energy savings potential that can be achieved by introducing power electronics into systems in the shown areas only is enormous: 25% of the current EU-25 electricity consumption.

| Application |                                | Electricity<br>consumption<br>[% of EU cons.] | Electrical energy saving potential              | Energy saving potential<br>[% of EU consumption] |

|-------------|--------------------------------|-----------------------------------------------|-------------------------------------------------|--------------------------------------------------|

|             | applications<br>s, HVAC, lifts | ~ 50%                                         | 30 - 40%<br>(feasible in ~ 50%<br>applications) | 5 - 6%                                           |

| Lighting    |                                | 21%                                           | > 70%                                           | > 14%                                            |

|             | Data centres<br>and servers    | 2%                                            | 50%                                             | 1%                                               |

| ICT         | Radio base<br>stations         | 1%                                            | 30%                                             | 0.3%                                             |

|             | Standby consumption            | 4%                                            | 80 - 90%                                        | 3.6%                                             |

Table 3-1 Power electronics applications and electrical energy-saving potential

#### Power electronics in the global view

*Table 3-2* shows several societal megatrends and their relation to power electronics. Some of these trends are enabled and only possible by using power electronics. Let us take a more detailed look at the role that power electronics plays in these trends.

| Megatrends                                             | Consequences for Power Electronics                                          |

|--------------------------------------------------------|-----------------------------------------------------------------------------|

| Mobility & Transport                                   | Hybrid and electric vehicles, urban transport, more electric aircraft/ships |

| Information & Communication Society                    | PC, internet, data servers, telecom, body area networks                     |

| Energy supply – security, availability and reliability | Energy efficiency, power quality, electrification, system reliability       |

| Energy-efficient buildings and homes                   | HVAC, lighting                                                              |

| Industrial manufacturing                               | Automation, process control, CAV                                            |

| Table | 3-2 Todays | megatrends | in | society |

|-------|------------|------------|----|---------|

|-------|------------|------------|----|---------|

#### **Mobility**

The transport sector is the fastest-growing sector in the European economy and, being responsible for above 30% of total primary energy consumption, represents the largest primary energy consumer in the EU. Final energy consumption in the transport sector grew 28.6% in the EU-25 between 1990 and 2004. Increasing fuel prices and the global energy situation have triggered worldwide investment in **electric and hybrid vehicles** and increasing penetration of these vehicles into the market. Power electronics is an enabling technology for the development of drive trains and battery-charging for these cleaner and more fuel-efficient vehicles. Furthermore, the increasing electrification of previously mechanical and hydraulic vehicle functions, such as x-by-wire applications like electric power steering or electric braking are only possible through the use of power electronics.

**Hybrid electric buses** using hybrid electric vehicle propulsion technology are increasingly becoming part of public transport in cities around the world. They offer considerable fuel savings, as high as 75% compared with a modern bus, and reduce emissions by as much as 60%. Power electronics is a necessary part of the drive train of these buses.

Aviation is responsible for ~12% of the transport energy consumption and is the fastest-growing energy consumer in the EU, with an increase of 73% between 1990 and 2006. Air transport demand is predicted to double in the next 10 - 15 years and triple in 20 years. **More electric aircrafts (MEAs)** where bleed air and hydraulic power sources are replaced with electrical equivalents, thus enabling a significant improvement in efficiency, system flexibility, aircraft reliability and specific fuel consumption, also depend on power electronics as an enabling technology. Boeing's More-Electric-Aircraft 787 Dreamliner has achieved a 20% reduction in fuel and CO<sub>2</sub> compared to its conventional counterpart 767 primarily due to its efficient no-bleed engines and the composite airframe. Power electronics systems are crucial for the aircraft's distributed power system and the total power electronic load is 1MW compared to several kW in conventional aircrafts.

#### Information and communication society

The impact of the information and communication society on the global economy has continuously increased over the last decades. The social benefits of this advance have also been translated into a proportional increase in the energy demanded by this sector.

In Western Europe the demand for IT services was about 60 TWh of electricity consumption (with another 20 TWh in the residential sector) and it is expected to rise to 104 TWh per year by 2020. In 2006, the power use associated with **servers and data centers**, including storage and network equipment, was about 1.5% of total US electricity consumption, and it is projected to increase to 2.5% of total electricity consumption by 2011. The peak load consumption of US data centers is around 8 GW, equivalent to 16 base-load power plants. The use of advanced power electronics techniques, like new DC distribution networks, can lead to a 10% reduction of the required energy. The integration of ICT technologies and power electronics, improving energy management, can yield an additional 20% energy saving, and the implementation of best practices can lead to a 50% reduction.

Today microprocessor industry is not only focused on the performance per euro but also on the performance per watt. Load consumption can be dramatically reduced by appropriate power supply strategy. Techniques like Dynamic Voltage Scaling that adjust the supply voltage of the microprocessor as a function of the work load can achieve significant reduction on the consumed power. Further improvements can be achieved increasing the efficiency of the power converters under light load conditions (e.g. when the processor is in idle mode) by means of reconfigurable power stage as a function of the load, adjustable digital control and optimization of dead times.

The annual electricity consumption related to **standby functionalities and off-mode** losses in the EU was estimated to be 47 TWh in 2005. Without taking specific measures, the consumption is predicted to increase to 49 TWh in 2020. An important portion of these losses is related to power supplies hence novel power electronics techniques for achieving high efficiencies at low loads are necessary. Further savings can be expected from the application of efficient power supplies in electronics appliances, such as TVs, VCRs, microwave ovens, etc.

It is estimated that European consumption of **broadband equipment** will be up to 50 TWh per year by 2015. Power amplifiers are one of the main building blocks of all modern wireless communications systems. They are used in all base stations and all the mobile units which are currently available. To maintain the required levels of system performance current commercially available amplifiers are designed to operate with extremely poor levels of efficiency, which means they consume far more energy than is strictly necessary. Power electronics techniques are also here crucial for reducing the energy consumption.

#### Energy supply – security, availability and reliability

The increasing energy demand, the shortage and finiteness of fossil fuels and the need for carbon footprint reduction in order to prevent hazardous climate changes have brought the issue of energy into the spotlight of political and public attention. Electrical energy is one of the cleanest, most efficient and versatile forms of energy and it is predicted that its demand will continue to grow at a much faster rate than other energy sources in the coming decades. In recent years there has been a growing awareness within the electricity supply industry of the need to reinvent Europe's electricity networks in order to meet the demands of twenty-first-century customers. In 2005 the European SmartGrids Technology Platform was established as a coherent approach to meet the challenges envisaged by network owners, operators and particularly users, across the EU. In the EC paper "Vision and Strategy for Europe's Electricity" it was concluded that future electricity markets and networks must provide all consumers with a highly reliable, flexible, accessible and cost-effective power supply, fully exploiting the use of both large centralised generators and smaller distributed power sources across Europe. End users will become significantly more interactive with both markets and grids; electricity will be generated by centralised and dispersed sources; and grid systems will become more inter-operable at a European level to enhance security and cost-effectiveness. This new concept of electricity networks is described as the 'SmartGrids' vision.

One of the priority actions of the EC Action Plan for Energy Efficiency is to make power generation and distribution more efficient. Transmission and distribution (T&D) losses of electrical energy are typically between 6% and 8%. Business Roundtable's Energy Task Force T&D Working Group, which ABB chairs, identified a number of energy-efficient technologies for grids, including power electronics technologies such as HVDC, FACTS, power electronic transformers, distributed generation/microgrids (power electronics is necessary to interface distributed generators such as wind turbines, solar cells etc. to the grid) etc. Power electronics has been identifies as a key technology in all four pillars of Smart Grids:

- Integration of renewables (wind turbine converters, HVDC for offshore wind park connection, SVC/STATCOM for grid code compliance, energy storage for improving stability and decreasing power fluctuations, solar converters etc.)

- **Integration of electric vehicles** ((fast) charging of electric vehicles, traction drive for hybrid (electric) vehicles, dynamic energy storage to absorb peaks due to simultaneous (fast) charging of electric vehicles)

- **Reliability and efficiency** (efficient long distance transmission with HVDC, variable speed drives in industrial plants and pumped hydro stations, energy storage for emergency and peak power, power quality solutions for industry etc.)

- **Demand response** (converter interface to distributed generation with built-in load management capability, drives in pumped hydro station with remote control from control centre).

#### Sustainable buildings and homes

Energy use in residential and commercial buildings is responsible for about 40% of the EU's total final energy consumption and CO2 emissions of which more than 50% is electrical energy. The cost-effective energy-saving potential by 2020 is significant: 30% less energy use within the sector is feasible. This equals a reduction of 11% of the EU's final energy use. The sector has significant untapped potential for cost-effective energy savings which, if realised, would mean an 11% reduction in total energy consumption in the EU by 2020.

**Smart Homes**, also known as automated homes, intelligent buildings, integrated home systems or domotics, have been gaining in popularity in the past few years. Smart homes incorporate common devices that control features of the home. Originally, smart home technology was used to control environmental systems such as lighting and heating, but recently the use of smart technology has developed so that almost any electrical component within the house can be included in the system. A reliable source of energy is mandatory for all these developments. Home energy management relying on power electronic systems is therefore one of the key issues for home automation. Such a distributed energy management would also interface the local renewable energy sources such as solar panels and the home loads.

**Energy-positive buildings** are those that generate more power than their needs. They include the management of local energy sources (mainly renewable, e.g. solar, fuel cells, microturbines) and the connection to the power grid in order to sell energy if there is excess or, conversely, to buy energy when their own is not sufficient. They use systems and components such as advanced Heating, Ventilating and Airconditioning (HVAC) and highly efficient lighting. They are equipped with intuitive devices that not only meter the energy consumed but also provide realtime information (e.g. on incentive pricing, deviations from standard consumption) to help people living in (or managing) these environments save energy while maintaining the desired comfort levels. They include Plug-in Electric Vehicles infrastructures in order to facilitate not only clean transport but also alternative local energy storage.

**Lighting** consumes more than 20% of all electricity generated in the European Union (EU). The situation is similar in the United States and the percentage is even higher in some developing

countries, since lighting is one of the largest uses of electric power. Power electronics is an enabling technology for new energy efficient lighting technologies. Gas discharge lamps such as fluorescent and HID lamps cannot be operated directly from the mains, because they have negative incremental impedance, and therefore, must be operated in series with current controlled ballast. To improve the efficiency of gas discharge lamps, the traditional magnetic ballasts can be replaced by high-efficiency electronic ballasts. The use of high-frequency electronic ballasts results in significant ballast volume and weight reduction and improves the performance of the discharge lamp. The high-frequency operation also makes the lamp start easily and reliably, and eliminates audible noise and flickering effects. In addition, due to the advances in power electronics, power regulation can be easily incorporated into the ballast, making intelligent energy management feasible. LED technologies and in some case plasma technology is being used for both indoor and outdoor next generation high efficiency lighting solutions and power electronics is playing a key role in developing high efficiency drivers for optimising their operation.

#### **Industrial manufacturing**

Nearly one-third of the world's energy consumption and 36% of its carbon dioxide (CO2) emissions are attributable to manufacturing industries. Manufacturing is still the driving force of the European economy, contributing over 6.500 billion euro in GDP. It covers more than 25 different industrial sectors, largely dominated by SMEs. There is an increasing demand for greener, more customised and higher quality products. The European manufacturing sector faces an intense and growing competitive pressure in global markets. European companies are faced with continuous competition in the high-tech sectors from other developed economies, such as the U.S, Japan and Korea. Manufacturing has to address the challenge of producing more products with less material, less energy and less waste. Together with other industrial technologies, ICT and advanced materials, power electronics-enabled variable-speed control of motors as an enabler for higher automation and better process control will improve the competitiveness of the companies. Power electronics in combination with wireless sensor technology can also be utilised for machine conditional monitoring applications, checking that electrical machines are operating in accordance with expected efficiency norms as well as enabling predictive maintenance to ensure machines are repaired/maintained in advance of breakdown thereby minimising downtime and associated losses.

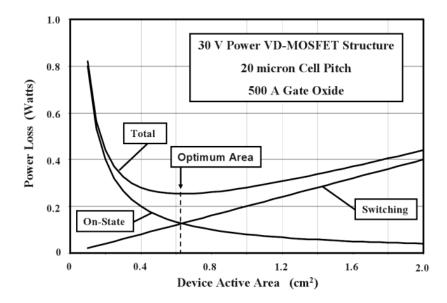

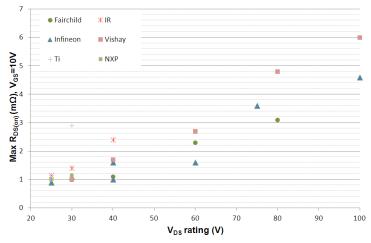

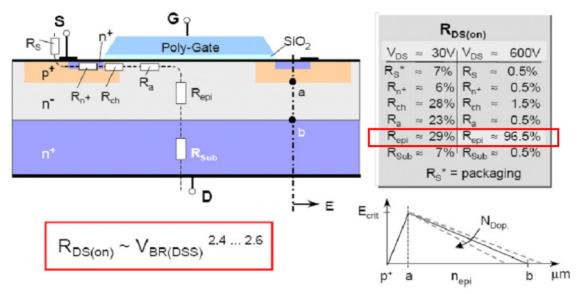

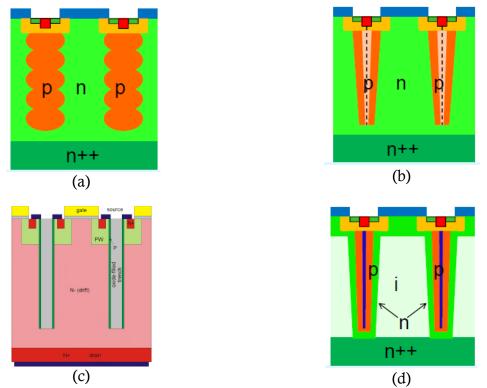

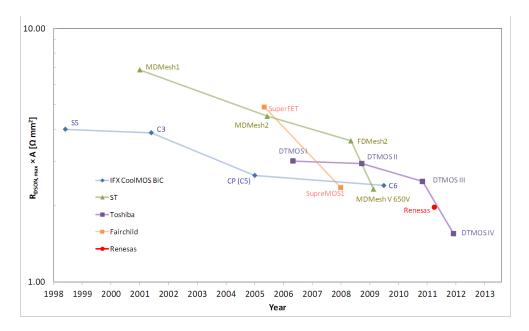

#### Conclusions