# CATRENE Programme Review Report 9

Cluster for Application and Technology Research in Europe on NanoElectronics

### **Full year report** January - December 2014

**Distribution list**

- CATRENE Board

- CATRENE Support Group

- CATRENE Steering Group Applications

- CATRENE Steering Group Technologies

- CATRENE Director's Committee

- CAPA

- CATRENE Office

.34

#### Table of Contents

| Executive Summary                                                                            | .7  |

|----------------------------------------------------------------------------------------------|-----|

| 1. Overview of CATRENE 1                                                                     | 1   |

| 2. 2014 CATRENE Year in Review 1                                                             | 17  |

| 2.1. Achievements                                                                            | 18  |

| 2.1.1. Reflection on a new tool for beyond 2015                                              | 18  |

| 2.1.2. Call 7                                                                                | 18  |

| 2.1.3. Increased links and cooperation with other Clusters/Programmes                        | 19  |

| 2.2. Events                                                                                  | 20  |

| 2.2.1. European Nanoelectronics Forum 2014 and CATRENE Innovation Award                      | 20  |

| 2.2.2. Common AENEAS and CATRENE Brokerage Event 2014                                        | 21  |

| 2.2.3. CATRENE Scientific Committee Workshop:<br>"Smart Systems for Healthcare and Wellness" | .21 |

| 2.2.4. CATRENE Design Technology Conference 2014                                             | 22  |

| 2.3. Publications                                                                            | 23  |

| 2.3.1. Project Profiles and Result Sheets                                                    | 23  |

| 2.3.2. Scientific Committee Report on Smart Systems for Health and Wellness                  | 23  |

| 2.4. Press Coverage                                                                          | 24  |

|                                                                                              |     |

| 3. Review of Call 7 and projects ended in 2014                                               | 29  |

| 3.1. Call 7 & unsolicited projects (labelled in 2014)                                        | 31  |

| 3.1.1. Overview Table                                                                        | 31  |

| 3.1.2. Project CAT120 CISTERN                                                                | 31  |

| 3.1.3. Project CAT121 EAST                                                                   | 32  |

| 3.2.1. Overview Table             |

|-----------------------------------|

| 3.2.2. Project CA303 OPTIMISE     |

| 3.2.3. Project CA402 THOR         |

| 3.2.4. Project CA308 ICAF         |

| 3.2.5. Project CA403 RELY         |

| 3.2.6. Project CT208 Reaching22   |

| 3.2.7. Project CT305 SOI450       |

| 3.2.8. Project CT306 NGC450       |

| 3.2.9. Project CT402 9D-Sense     |

| 3.2.10. Project CT210 Dynamic-ULP |

|                                   |

3.2. Projects ended in 2014

3.1.6. Project CAT601 SiPoB-3D

### 4. Appendices

Appendix A. CATRENE Projects Focus Matrix

Appendix B. Glossary of Terms

3.1.4. Project CAT209 H20

3.1.5. Project CAT406 NEMADE

|   | 3.1.6. Project CAT601 SiPoB-3D    | 35 |

|---|-----------------------------------|----|

|   | 3.1.7. Project CAT801 TSV-HANDY   | 36 |

|   | 3.1.8. Project CAT802 SAM3        |    |

| r | rojects ended in 2014             |    |

|   | 3.2.1. Overview Table             | 40 |

|   | 3.2.2. Project CA303 OPTIMISE     | 40 |

|   | 3.2.3. Project CA402 THOR         | 42 |

|   | 3.2.4. Project CA308 ICAF         |    |

|   | 3.2.5. Project CA403 RELY         | 45 |

|   | 3.2.6. Project CT208 Reaching22   |    |

|   | 3.2.7. Project CT305 SOI450       | 47 |

|   | 3.2.8. Project CT306 NGC450       |    |

|   | 3.2.9. Project CT402 9D-Sense     | 50 |

|   | 3.2.10. Project CT210 Dynamic-ULP |    |

|    |  |  |  |  |  |  |  |  |  |  | ( |  |

|----|--|--|--|--|--|--|--|--|--|--|---|--|

|    |  |  |  |  |  |  |  |  |  |  |   |  |

| 61 |  |  |  |  |  |  |  |  |  |  |   |  |

## **Executive Summary**

#### **EXECUTIVE SUMMARY**

CATRENE (Cluster for Application and Technology Research in Europe on Nano-Electronics) is a EUREKA cluster programme dedicated to cooperative research in micro and nanoelectronics.

The CATRENE cluster programme ( $\Sigma$ ! 4140) was approved by the EUREKA conference in Maribor on 25 October 2007, officially announced at the Ministerial Conference in Ljubljana on 06 June 2008, and started 01 January 2008 as a four year programme until year-end 2011. It has been extended until the end of 2015.

The following European Member States actively support CATRENE: Austria, Belgium, France, Finland, Germany, Ireland, Israel, Spain, Sweden, The Netherlands and Turkey.

The 2014 CATRENE Programme Review will cover the progress and actions undertaken throughout the year to meet the programme's objective, which is to foster technological Leadership for a competitive European ICT.

Chapter 1 provides an overview of the CATRENE programme while chapter 2 and 3 focus more specifically on 2014 projects and actions.

#### **Overview of CATRENE**

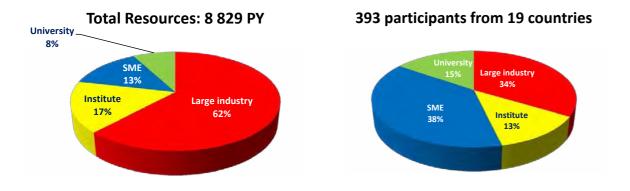

The CATRENE programme opened its 1st Call for Project Proposals on 29 February 2008. Today, a total of 7 calls have been launched resulting in 66 labelled projects and a total effort of 8 829 PYs.

At the end of 2014, 23 CATRENE projects had successfully ended.

#### Results of CATRENE Call 7 and launch of CATRENE Call 8

In 2014, CATRENE launched its 7th Call for Project Proposals. Altogether, 7 projects were labelled amounting to 799 PYs.

It is of interest to note that SAM3 and SIPOB-3D have been co-labelled by CATRENE and EURIPIDES<sup>2</sup>.

#### **European Nanoelectronics Forum 2014**

The seventh edition of the European Nanoelectronics Forum took place in Cannes, France, on 26-27 November 2014 under the theme *Enabling Smart Solutions*.

Jointly organized by AENEAS, the EUREKA Cluster CATRENE, the ECSEL Joint Undertaking and the European Commission, the event had a good participation of 270 attendees from all over Europe.

During the forum, the project EM4EM received the CATRENE Innovation Award for its outstanding results which are pre-conditions for the next generation of electric vehicles, allowing European companies in the automotive industry to secure and expand while preserving or even increasing employment in Europe.

The feedback received in the questionnaire sent to participants at the end of the event showed a very high level of satisfaction, in particular with regards to the setup of the Project Village and

to the richness of the programme.

In addition to the day to day activities in 2014, reflection on a new tool for beyond 2015 was addressed. Industry proposed to start a new EUREKA cluster for micro and nanoelectronics. A dedicated Joint Working Group between National Authorities and Industry, which had the mandate to develop a concept for a new cluster, formulated new ideas for the scope and the organisation - based on the recommendations in the assessment report and the feedback received through interviews with the European Electronic Components and Systems community. A first draft was presented and discussed at the common meeting between National Authorities and Industry in April 2014.

At the same time, the new ECSEL Joint Undertaking was started by the European Commission and the Member States, focusing on the value chain from micro and nanoelectronics until System Integration. The requirement of the Public Authorities was to show that the planned new EUREKA Cluster and ECSEL are complementary tools - while having overlaps in content. During the year 2014, a lot of effort was put into the preparation of the concept for the New Tool. The concept was presented to the Public Authorities in November 2014. A detailed reaction with "cornerstones" for the New Tool is expected early 2015. The final decision on the establishment of a New EUREKA Cluster for micro and Nanoelectronics will most probably be taken in March 2015.

## **Overview of CATRENE**

#### **1. Overview of CATRENE**

The CATRENE programme opened its 1st Call for Project Proposals on 29 February 2008. Today, a total of 7 calls have been launched resulting in 66 labelled projects. By the end of 2014, 23 CATRENE projects had successfully ended.

| Out of the labelled are: |                |                |          |                                                    |                       | re:    |

|--------------------------|----------------|----------------|----------|----------------------------------------------------|-----------------------|--------|

| Call                     | PO<br>received | FP<br>received | Labelled | Cancelled<br>/merged/<br>transferred/<br>suspended | Successfully<br>Ended | Active |

| 1 <sup>st</sup> Call     | 18             | 15             | 14       | 5                                                  | 9                     | 0      |

| Applications             | 10             | 8              | 8        | 3                                                  | 5                     | 0      |

| Technologies             | 8              | 7              | 6        | 2                                                  | 4                     | 0      |

| 2 <sup>nd</sup> Call     | 14             | 10             | 10       | 3                                                  | 7                     | 0      |

| Applications             | 9              | 7              | 7        | 3                                                  | 4                     | 0      |

| Technologies             | 5              | 3              | 3        | 0                                                  | 3                     | 0      |

| 3 <sup>rd</sup> Call     | 15             | 10             | 10       | 3                                                  | 6                     | 1      |

| Applications             | 7              | 4              | 4        | 2                                                  | 2                     | 0      |

| Technologies             | 8              | 6              | 6        | 1                                                  | 4                     | 1      |

| 4 <sup>th</sup> Call     | 19             | 14             | 10       | 1                                                  | 1                     | 8      |

| Applications             | 10             | 8              | 7        | 1                                                  | 0                     | 6      |

| Technologies             | 9              | 6              | 3        | 0                                                  | 1                     | 2      |

| 5 <sup>th</sup> Call     | 8              | 5              | 5        | 1                                                  | 0                     | 4      |

| Applications             | 5              | 3              | 3        | 0                                                  | 0                     | 3      |

| Technologies             | 3              | 2              | 2        | 1                                                  | 0                     | 1      |

| 6 <sup>th</sup> Call     | 13             | 10             | 9        | 2                                                  | 0                     | 7      |

| Applications             | 9              | 7              | 6        | 1                                                  | 0                     | 5      |

| Technologies             | 4              | 3              | 3        | 1                                                  | 0                     | 2      |

| 7 <sup>th</sup> Call     | 9              | 9              | 8        | 1                                                  | 0                     | 7      |

| Applications             | 5              | 5              | 4        | 1                                                  | 0                     | 3      |

| Technologies             | 4              | 4              | 4        | 0                                                  | 0                     | 4      |

| Per end of<br>2014       | 96             | 73             | 66       | 16                                                 | 23                    | 27     |

Over the course of the entire CATRENE programme, a total of 16 projects were cancelled/merged due to national eligibility criteria, funding constraints and in some countries even as a result of reduced funding volume. In 2014, two projects (1 from Applications and 1 from Technologies) labelled during the 6th Call were cancelled due to funding issues.

Resources, participants and work areas

The following graphs provide an overview of the CATRENE project resources (in PYs), of their participants and of their related work area.

#### CATRENE Calls 1 to 7 labelled resources Total PYs: 8829\*

\*This figure does not include the person years of MEDEA+ projects which continued running until 2010.

#### CATRENE resources per country as per year end 2014

| 50 pi    | rojects, 393 partners             |

|----------|-----------------------------------|

| 25 19 pa | articipating countries            |

| K        | Total for 2009-2018:<br>8 829 PYs |

| *        | AUT: 252<br>BEL: 219<br>CHE 2     |

|          | CZE: 26<br>DEU: 1363<br>ESP: 243  |

| ~        | FIN: 16<br>FRA: 4285              |

| 32       | GBR 3<br>HUN: 1<br>IRL: 75        |

| restry   | ITA: 112<br>NLD: 2014<br>NOR: 5   |

| 5        | PRT: 97<br>ROU: 3<br>SWE: 26      |

| 21       | TUR: 66                           |

| 7        | Non-European country<br>ISR: 21   |

CATRENE labelled projects - split by work area

For a more detailed list of projects according to work areas, see Appendix B. CATRENE projects focus matrix at the end of this document.

## CATRENE Year in Review

#### 2. 2014 CATRENE Year in Review

#### 2.1. Achievements

#### 2.1.1. Reflection on a new tool for beyond 2015

Industry proposed to start a new EUREKA cluster for micro- and nanoelectronics. A dedicated Joint Working Group between National Authorities and Industry, which had the mandate to develop a concept for a new cluster, formulated new ideas for the scope and the organisation - based on the recommendations in the assessment report and the feedback received through interviews with the European Electronic Components and Systems community. A first draft was presented and discussed at the common meeting between National Authorities and Industry in April 2014.

At the same time, the new ECSEL Joint Undertaking was started by the European Commission and the Member States, focusing on the value chain from micro- and nanoelectronics until System Integration. The requirement of the Public Authorities was to show that the planned new EUREKA Cluster and ECSEL are complementary tools - while having overlaps in content. During the year 2014, a lot of effort was put into the preparation of the concept for the New Tool. The concept was presented to the Public Authorities in November 2014. A detailed reaction with "cornerstones" for the New Tool is expected early 2015. The final decision on the establishment of a New EUREKA Cluster for micro and Nanoelectronics will most probably be taken in March 2015.

#### 2.1.2. Call 7

In 2014, CATRENE launched its 7th Call for Project Proposals. The call opened with a Brokerage Event on 05-06 February in Brussels, attended by more than 200 people from across Europe. During the event, more than 40 project ideas for CATRENE and the ENIAC JU were identified and elaborated on.

| Call opens                    | 04 February  | Labelling sessions |

|-------------------------------|--------------|--------------------|

| PO submission ends            | 05 April     | 22 October         |

| Communication on selected POs | 25 May       | 25 November        |

| FP submission opens           | 01 June      |                    |

| FP submission ends            | 04 September |                    |

Altogether, 7 projects were labelled by CATRENE as a result of CALL 7 amounting to 799 PYs.

| Call # | Project<br>Number | Acronym   | Work Area                                 | PYs |

|--------|-------------------|-----------|-------------------------------------------|-----|

| 7      | CAT120            | CISTERN   | Communication & Digital Lifestyles        | 116 |

| 7      | CAT121            | EAST      | Communication & Digital Lifestyles        | 193 |

| 7      | CAT209            | H2O       | Safety and Security                       | 206 |

| 7      | CAT406            | NEMADE    | Health and the Ageing Society             | 15  |

| 7      | CAT601            | SIPOB-3D  | Design Technology                         | 102 |

| 7      | CAT801            | TSV-HANDY | Equipment, Materials and<br>Manufacturing | 50  |

| 7      | CAT802            | SAM3      | Equipment, Materials and<br>Manufacturing | 117 |

It is of interest to note that SAM3 and SIPOB-3D have been co-labelled by CATRENE and EURIPIDES<sup>2</sup>.

More details on the projects labelled in Call 7 are available in Chapter 3 of this publication.

#### 2.1.3. Increased links and cooperation with other Clusters/Programmes

The mission of CATRENE is to promote and to strengthen the European nanoelectronics R&D&I community. CATRENE and other EUREKA Clusters have been recognised as the only initiatives directly managed by R&D&I actors in regular contact with the EUREKA network and Public Authorities.

According to its mission, CATRENE is cooperating with other initiatives and organisations supporting the nanoelectronics domain:

- CATRENE and its predecessor programmes exists since 1987 and has continuously collaborated with the other EUREKA Clusters.

- CATRENE has co-labelled projects with other EUREKA Clusters and European funding programmes.

- An Inter-Cluster Committee has been created in 2010 to reinforce this cooperation.

- CATRENE has a strong link with the industry association "AENEAS" representing R&D&I actors in the ECSEL JU.

- CATRENE and AENEAS work together to define a common 'Vision, Mission and Strategy' (VMS) the reference document for projects in CATRENE, ENIAC JU and the ECSEL JU.

- CATRENE and AENEAS host a Common Brokerage Event each year to prepare upcoming CATRENE and ECSEL calls.

- CATRENE organises the annual European Nanoelectronics Forum with the contribution of

the AENEAS, ECSEL JU and DGConnect (FP7) where projects and speakers from the three programmes are presented.

#### 2.2. Events

A number of events underlined the CATRENE communication strategy in 2014, reaching from the very technically oriented and network focused Brokerage Event for experts to the yearly European Nanoelectronics Forum, which has achieved a high level of recognition in Europe today.

#### 2.2.1. European Nanoelectronics Forum 2014 and CATRENE Innovation Award

The European Nanoelectronics Forum 2014 took place in Cannes, France on 27-28 November. 270 participants from all over Europe attended the event organised under the theme *Enabling Smart Solutions*. During the plenary session, the audience showed high appreciation for the speeches delivered, notably by Ben Verwaayen (Chairperson of the ELG), Philip Moynagh (Intel) and Berthold Hellenthal (Audi). The Project Village was organised in an area of 850 m<sup>2</sup> and presented 70 projects from CATRENE, the ENIAC JU and the European Commission's FP7 programme. The new setup of the village, compared to previous years, was optimised to favour discussion and networking. A total of 4 Speakers' Sessions were organised in the exhibition area during which hot topics were presented in an informal setting. The high number of participants in the sessions was unforeseen (15 participants per session in 2013 compared to +/-80 in 2014) and as a consequence the set up was not optimal. This will be corrected for 2015.

The feedback received in the questionnaire sent to participants at the end of the event showed a high level of satisfaction and that expectations were met at 95%.

The event was jointly organised by AENEAS, CATRENE, the ECSEL Joint Undertaking and the European Commission.

During the event, the project EM4EM (ElectroMagnetic reliability of electronic Systems for Electro Mobility) was chosen 2014 winner of the CATRENE Innovation Award. The results of the project are pre-conditions for the next generation of electric vehicles, allowing European companies in

the automotive industry to secure and expand while preserving or even increasing employment in Europe.

The objective of the EM4EM consortium is to cut out this interference as much as possible while extending its impact to the development of electronics that are better able to withstand electromagnetic interference. With a strong interdisciplinary consortium led by Audi and including automotive manufacturers, suppliers, semi-conductor manufacturers from three European countries, as well as universities, the EM4EM project has already produced impressive results. EM4EM deliverables (including tried and tested models, measurement methods and procedures as well as simulation tools) will benefit a large number of European businesses by reducing time-to-market and costs of EMR-optimised components and systems for electric vehicles. The demonstrators along the value chain, for example, will help third parties integrate these results quickly into new products.

The CATRENE Innovation Award is bestowed each year to a project with a high level of innovation and far-reaching exploitation potential, market impact and overall benefits for Europe, as well as, creative objectives and effective management.

The next European Nanoelectronics Forum will be held on 01-02 December 2015.

#### 2.2.2. Common AENEAS and CATRENE Brokerage Event 2014

The AENEAS/CATRENE Common Brokerage Event 2014 took place in Brussels, Belgium on 05-06 February and was held back-to-back with the ARTEMIS-IA Brokerage Event. Every year, the event brings together the European Nanoelectronics Community, to generate ideas for project proposal for the next CATRENE and ECSEL calls and to start consortia preparations.

The programme of the event is based on sessions covering the work areas common to both the CATRENE White Book and the ECSEL JU MASP:

- Communication and Digital Lifestyles

- Automotive and Transport

- Energy Efficiency

- Safety and Security

- Health and the Ageing Society

- Design Technologies

- Equipment, Materials and Manufacturing

- Semiconductor Process and Integration

During each session, a designated leader moderates the discussion around new project ideas along with consortia building.

During the 2014 edition, more than 230 participants worked together over the 2 days of the event coming up with more than 40 preliminary project ideas.

#### 2.2.3. CATRENE Scientific Committee Workshop

"Smart Systems for Healthcare and Wellness"

See 2.3.2

#### 2.2.4. CATRENE Design Technology Conference 2014

The CATRENE Design Technology Conference was held in June 2014 in Grenoble. It was carried out in conjunction with the Leti Days Conference.

73 Delegates belonging to 30 different organisations and coming from 6 European countries (Austria, Finland, France, Germany, The Netherland, and Spain) attended the conference. The mix of representatives from industry and academic creates ideal opportunities for a professional exchange of ideas on a scientific basis.

The focus of the event was on application-oriented design methods for micro- and nanoelectronic products.

Based on this, DTC was organised into 5 Technical Sessions:

- 1. Reliability of SoCs in Safety Critical Applications

- 2. Power and thermal aware design

- 3. Energy efficient HPC

- Power Electronics 4.

- 5. Design enablement for advanced silicon technologies

#### and 2 Panels:

- What are the next growth areas in multimedia beyond TV, mobiles phones/tablets, STB,...? •

- ٠ EDA beyond IC design

Held annually, the CATRENE DTC has become the meeting point for Europe's scientists and experts in applications-oriented design. It is a unique opportunity to meet the CATRENE projects researchers while enjoying the high quality program of the conference. However, attendees all agree that the best thing about DTC is the technical results which are presented by real experts from the field. The confluence of academic and industrial perspectives as well as electronic system design and manufacturing perspectives is unlike any other conference.

#### 2.3. Publications

#### 2.3.1. Project Profiles and Result Sheets

As of the end of 2014, 34 CATRENE Project Profiles and 16 CATRENE Result Sheets have been produced and published on the web.

#### 2.3.2. Scientific Committee Report on Smart Systems for Health and Wellness

The CATRENE Scientific Committee released the 'Smart Systems for Health and Wellness' report in February 2014 during a workshop in Brussels that gathered close to 80 participants.

The report and workshop focused on the key role that micro- and nanotechnology can play in finding solutions for this problem. Over the last 60 years, semiconductor technology has progressed tremendously. Following Moore's law, huge computation power has become available into handheld devices, sensors have shrunk in size, and wireless communication has penetrated into the consumer market, to name only a few developments. The next step is the migration into wearable devices. Already many products are appearing on the market, but with limited functionality and unfit for long term continuous monitoring. More research is needed to obtain that goal. This report will focus on the technology challenges that still lie ahead, and discuss possible solutions.

Various technologies are reviewed in the report with the following keywords in mind: prevention (including the promotion of healthy lifestyle through fitness and stress monitoring), diagnostic, therapy and therapy monitoring as well as decentralization from hospital to home maintenance. Three large applications are targeted: Devices for the healthy, devices to cure, and devices to aid the chronically ill ("stay fit", "get well", "a better live"). They have to operate unobtrusive, need full autonomy and are either wearable or implantable. Small devices (cm to mm size), with a typical power budget between several µW and a few mW are envisaged.

The report received a high level of support from Industry and is available for download on the CATRENE website.

### 2.4. Press Coverage

The overview of 2014 press coverage is available on the CATRENE website in the communication section under Press Clips, and includes a link to view the complete text.

| Article                                                                                                       | Source        | Country | Year 2014 |

|---------------------------------------------------------------------------------------------------------------|---------------|---------|-----------|

| 5 milliards d'euros pour la R&D<br>européenne en nanoélectro-<br>nique et systèmes embarqués<br>d'ici 2020    | ElectroniqueS | FRA     | January   |

| Avec Ecsel, l'Europe devra pas-<br>ser du développement à la com-<br>mercialisation de produits               | ElectroniqueS | FRA     | January   |

| edaWorkshop und CATRENE DTC<br>2013 - Ein Rückblick                                                           | edacentrum    | DEU     | January   |

| European Nanoelectronics<br>Forum: Innovation for growth                                                      | edacentrum    | DEU     | January   |

| A breakthrough in EUV<br>technology                                                                           | EUREKA News   | BEL     | February  |

| Denis Rousset directeur du<br>bureau Catrene, cluster Eureka<br>dédié à la nanoélectronique                   | ElectroniqueS | FRA     | 24 March  |

| Gérard Matheron (Acsiel): «Il<br>faut assouplir les règles euro-<br>péennes sur les subventions<br>publiques» | ElectroniqueS | FRA     | 21 May    |

| Jean-Luc Maté devient président<br>du comité Intercluster d'Eureka                                            | ElectroniqueS | FRA     | 20 June   |

| Le projet Thor ouvre des débou-<br>chés prometteurs pour les com-<br>posants en carbure de silicium           | ElectroniqueS | FRA     | 3 July    |

| Article                                                                                           | Source             | Country | Year 2014   |

|---------------------------------------------------------------------------------------------------|--------------------|---------|-------------|

| 10 new innovative nanoelec-<br>tronics projects in EUREKA<br>CATRENE's pipeline                   | EUREKA News        | BEL     | 1 August    |

| The Importance Of Kitchen<br>Tables And Pubs                                                      | Electronics Weekly | GBR     | 26 November |

| EC IC Manufacturing Boost May<br>Need Foreign Investment                                          | Electronics Weekly | GBR     | 26 November |

| There's Still Hope                                                                                | Electronics Weekly | GBR     | 26 November |

| EC will support foreign semi<br>manufacturers if locals won't<br>invest                           | Electronics Weekly | GBR     | 26 November |

| Ledproject met grote<br>Nederlandse inbreng wint in-<br>novatieprijs Eniac                        | Bits&Chips         | NLD     | 27 November |

| Die letzte Chance nutzen                                                                          | elektroniknet      | DEU     | 27 November |

| Der finanzielle Rahmen ist<br>geschaffen                                                          | elektroniknet      | DEU     | 27 November |

| IoT Gets Woolly In Cannes                                                                         | Electronics Weekly | GBR     | 27 November |

| Increasing SME involvement in EC R&D programmes                                                   | Electronics Weekly | GBR     | 27 November |

| Europe Must Fund First<br>Production Fabs, says Chery                                             | Electronics Weekly | GBR     | 28 November |

| European Nanoelectronics<br>Forum a real success for<br>EUREKA nanoelectronics Cluster<br>CATRENE | EUREKA News        | BEL     | 18 December |

| Zuken Plays Key Role in<br>Innovation Award Win for<br>Electric Vehicle Research<br>Collaboration | Zuken              |         | 19 December |

| Article                                                                                                                                                                                                                                                     | Source           | Country | Year 2014 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------|-----------|

|                                                                                                                                                                                                                                                             | Industry News    |         |           |

| Précédent   L'Europe de<br>l'industrie et du numérique à<br>l'heure des choix politiques  <br>Suivant Usine Digitale > Semi-<br>conducteurs L'Europe ne fait<br>rien pour soutenir la produc-<br>tion dans les semi-conducteurs,<br>s'indigne la profession | L'Usine Digitale | FRA     | 20 May    |

# Review of Call 7 & Projects Ended in 2014

#### 3. Review of Call 7 and projects ended in 2014

A total of 9 Project Outlines leading to 9 Full Proposals were received in 2014. From these 9 proposals, 8 were labelled and one withdrew.

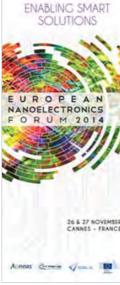

The Call 7 projects amount to a total effort of 799 Person Years. The countries contribution is dominated by France with 45% of the efforts followed by Germany and The Netherlands with respectively 20% of the total efforts as illustrated in the Figure 1 below.

#### Figure 1: Call 7 labelled projects - PYs per country

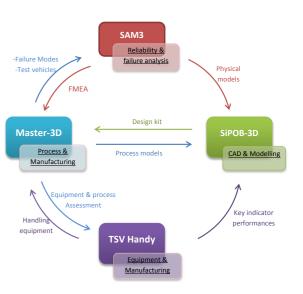

Concerning technologies, the projects are clearly orientated along the More than Moore axis, with as first topic of interest the 3D IC and 3D system in package. In particular, the Call 7 covers the problematics of design tools, wafer handling equipment and failure analysis instruments for these new generations of ICs (see Figure 2 for relationship between these projects and their respective domains). Always along the More than Moore axis, the Call addresses the challenge of RF function integration in RF frond end SoC for the fifth generation of mobile network.

Regarding applications, security in the Internet of Things is a strong thematic addressed in this Call through the development of secure wearable objects. The development of new generations of CMOS image sensors for healthcare, security, entertainment and automotive is gathering the rest of the effort.

#### Ending projects

Over the course of 2014, 9 projects ended with a majority belonging to the third Call of CATRENE. It is important to note that 2014 has seen the end of all CATRENE projects focusing on 450mm.

### 3.1. Call 7 & unsolicited projects (labelled in 2014)

3.1.1. Overview Table

| Call # | Project<br>Number | Acronym   | Work Area                                 | PYs |

|--------|-------------------|-----------|-------------------------------------------|-----|

| 7      | CAT120            | CISTERN   | Communication & Digital Lifestyles        | 116 |

| 7      | CAT121            | EAST      | Communication & Digital Lifestyles        | 193 |

| 7      | CAT209            | H2O       | Safety and Security                       | 206 |

| 7      | CAT406            | NEMADE    | Health and the Ageing Society             | 15  |

| 7      | CAT601            | SIPOB-3D  | Design Technology                         | 102 |

| 7      | CAT801            | TSV-HANDY | Equipment, Materials and<br>Manufacturing | 50  |

| 7      | CAT802            | SAM3      | Equipment, Materials and<br>Manufacturing | 117 |

#### 3.1.2. Project CAT120 CISTERN

Cmos Image Sensor Technologies' Readiness for Next generation of applications

Project leader: Klaas Jan Damstra (Grass Valley)

#### Brief description:

The objective of CISTERN is to address societal needs in the areas of security, and entertainment. These societal needs include citizens' security through Ultra High Definition surveillance systems, intelligent security systems through 3D vision, image capture for the first generation of Ultra High Definition Television, and sorting in the food industry. CISTERN addresses these needs by improving the performance of advanced image capturing systems (imagers) such as time-of-flight cameras, highresolution/high sensitive and hyper- and multispectral security cameras, and broadcast cameras. Improved image quality allows for the extraction of more detailed information and a wider range of applicability.

In particular, the goal of the CISTERN project is:

To develop CMOS imager sensors with improved performance on spatial resolution, temporal resolution, higher bit depths, lower noise, wider colour gamut, higher quantum efficiency (not necessarily all combined for each sensor) and additional, smart functionality in the pixels. The consortium will develop imager sensors in the categories UHDTV, Time-of-Flight and hyper- and multi-spectral, for the application areas broadcast, entertainment, and security.

- To develop real time image processing techniques needed to improve the quality of the digital output signal of the sensor demonstrators.

- To develop and demonstrate the capability to produce multispectral imagers by hybridization of multispectral filter arrays on top of CMOS sensor. Both matrix filters and hybrid assembly process will be developed within the project.

- To demonstrate the improved performance of the CMOS imagers combined with related processing in a number of demonstrators.

- To develop Ultra High resolution, widely opened, sensor adapted zoom lenses (2/3" format, 4K resolution) for broadcast and security applications/markets.

- To optimize lens design in term of performance/cost/weight/camera integration for integral imaging chains.

- To develop and demonstrate an integrated Camera Lens Assembly for security applications that offers UHDTV performance with Size and Weight of an HDTV solution.

- To start in-house CMOS image sensor development in Grass Valley.

This project will build strong links with the ECSEL JU project EXIST.

Countries: Belgium, France, The Netherlands

#### Partners:

| Belgium         | SoftKinetic Sensors                                                                        |

|-----------------|--------------------------------------------------------------------------------------------|

| France          | Le2i-University of Burgundy,<br>SILIOS Technologies (sub-contractor of<br>Le2i),<br>Thales |

| The Netherlands | Adimec,<br>Grass Valley,<br>TU Delft                                                       |

Expected start date: 01-04-2015 Expected end date: 31-03-2018

#### 3.1.3. Project CAT121 EAST

Smart Everything everywhere Access to content through Small cells Technologies

#### Project leader: Philippe Meunier (NXP Semiconductors)

#### Brief description:

Today the wireless user is served by powerhungry 2G/3G/4G macro/micro-cell base stations still having bounds on their data capacity, while the available spectrum has become a scarce resource. Fifth-generation (5G) mobile networks based on more and low power cells are expected to overcome these limitations and truly enable smart, high-speed, everything everywhere access to their end users. In these low power networks, the technology for base station will have much more similarities to those of the handsets compared to the situation in 3G/4G applications.

However, to make the small cells network solution successful technically and commercially for 5G, the following requirements on the RF front ends part of the Base station and handset have to be fulfilled:

- 1. Drastic cost & size reduction through integration;

- 2. Reduced energy consumption;

- 3. Improved re-configurability, adaptability and MIMO functionality.

EAST responds to these constraints for 5G networks up to 6GHz, working on technologies, packaging, signal processing, architecture design, and modelling for both base stations and mobiles. This clear focus on the "low" GHz range addresses the general expectation that this market segment will represent the highest economic value with the lowest environmental (energy consumption) impact. In particular, to fulfil the first requirement endowing cost reduction and miniaturization, EAST will research on:

- The high-density integration capabilities of CMOS/BiCMOS silicon technologies for the integration of antenna switch, low noise amplifiers and medium noise amplifiers;

- New packaging technics handling at the same time low insertion losses and good thermal dissipation.

Concerning energy saving, EAST will propose solution in the field of:

- Signal processing algorithms, to decrease computational power in the digital predistortion process;

- Technologies, exploiting the much better power-handling capabilities of LDMOS.

For the last field of requirement EAST will work on:

- Design, with fully digital Tx solution, enabling easy reconfiguration;

- Architecture for antenna array, enabling the MIMO capability.

Countries: France, Ireland, The Netherlands, Portugal

#### Partners:

| France  | 3DiS Technologies,<br>AMCAD Engineering,<br>Cassidian,<br>CEA-LETI,<br>Ethertronics,<br>III-V LAB,<br>IMS Laboratory-University of Bordeaux,<br>Institut Mines-Telecom/Telecom Paris-<br>Tech,<br>NXP Semiconductors,<br>Sequans Communications,<br>Thales Communications & Security,<br>XLIM Xlim |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ireland | Alcatel-Lucent                                                                                                                                                                                                                                                                                     |

| The Netherlands | Anteverta-mw,<br>Besi,<br>Bruco Integrated Circuits,<br>Delft University of Technology,<br>NXP Semiconductors,<br>TNO,<br>TUE - Technical University of Eindhoven |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Portugal        | GSLDA,<br>Instituto de Telecomunicacoes,<br>NANIUM                                                                                                                |

Expected start date: 01-04-2015 Expected end date: 31-03-2018

#### 3.1.4. Project CAT209 H2O

Human to Objects "Easy Interactions in the Smart City"

Project leader: Christian Dietrich (Gemalto)

Brief description:

The purpose of the H2O project, capitalizing on former results from the CATRENE eGo project, is to develop the requested architecture to put the human in control of the smart objects surrounding, put on or in him, so as to develop a human centric and privacy ensuring security architecture to support the rapidly emerging Wearable computing and IoT markets. The project will investigate the human to object interactions in different application areas of the smart city domain: communication, transportation, e-health and e-retail. The purpose of this work will be to study and implement advanced architecture concepts and technology bricks felt as missing for the deployment of efficient wearable computing solutions, as resulting from the former successfully ended eGo project and also to develop new user experience for a complete adoption of this new digital lifestyle. The major assets delivered by the project will be:

• A high-performance, reliable, ultralow-power BCC (Body Communication Coupling) technology with a standardized physical layer which should be usable as

communication enabler in any Body Area Network. The eGo project has demonstrated the need to improve the BCC interface for addressing harsh environments.

- A representative set of non-intrusive, secure, low-cost, always working, wearable devices, suitable for several application domains pertaining to the IoT or smart-city area (in particular, ehealth, communication, safety and security, and retail). The eGo project has prototyped some form factors acceptable by a large category of users, and the project intend to implement robust and easy-to-use form factors (e.g. bracelet, clips...) suitable for the target applications.

- ٠ A fully trusted and privacy preserving transaction environment, enabling the object(s) that the user wears or can touch to seamlessly initiate applications or communication with or between objects.

- An Open SDK and application certification tool-chains enabling third party developers to easily develop apps for wearable and guarantying that such app can be automatically verified before being remotely loaded in the wearable devices owned by the user.

- To complete reference and trusted security architecture enabling seamless secure synchronization of wearable devices. This synchronization includes the recovery of credentials into a blank wearable device.

- To pilot implementation of wearable computing scenarios in some IoT or Smart-City application domains, together with first QoS or QoE feedback reports.

Countries: Czech Republic, France, Ireland, Portugal

#### Partners:

| Czech Republic | IMA - Institute of Microelectronic Applica-<br>tions                                                                                                                |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| France         | ASTUS,<br>CEA–LETI,<br>CEA LIST,<br>Gemalto,<br>IDATE,<br>Insight SiP,<br>Oberthur Technologies,<br>SORIN CRM,<br>STMicroelectronics,<br>Trusted Labs,<br>Worldline |  |

| Ireland        | Electro Automation,<br>InHandGuides,<br>Institute of Technology Cork,<br>Tyndall National Institute                                                                 |  |

| Portugal       | GSLDA,<br>Instituto de Telecomunicacoes                                                                                                                             |  |

Expected start date: 01-12-2014 Expected end date: 30-11-2017

#### 3.1.5. Project CAT406 NEMADE

New Mammography Detector

Project leader: Jan T. Bosiers (Teledyne DALSA)

#### Brief description:

This project aims at developing a new generation, multi-modality (screening, biopsy and tomosynthesis) mammography detector, bringing better imaging performance at lower X-ray dose and higher patient comfort, at a lower cost. The incumbent technology is at a point where it can no longer meet new application and regulatory requirements like higher speeds, multi-modality and lower patient X-ray dose. The improved sensitivity and precision of the new generation detectors will also enable improved treatment. As benchmark, the current detectors for mammography are considered. Access to clinical validation is secured via SigmaScreening through co-founder Prof. Dr. Den Heeten who works at the Department of Radiology of in the Academic Medical Center (AMC) in Amsterdam, or by clinical trials by a selected OEM.

The five main technical goals are:

- 1. More efficient X-ray energy conversion and improved image contrast by improved scintillator performance;

- 2. Detector using newest generation CMOS imagers allowing additional features like switchable saturation dose, dual-energy compatibility and real-time X-ray dose sensing and control; and improved imaging processing capabilities;

- 3. Improved assembly technology matching the stringent requirements for high-resolution mammography applications, combined with high reliability;

- More personalized mammography and 4. higher patient safety by adaptive breast compression, reduced X-ray dose and shorter imaging cycles, fewer re-takes, fewer incorrect screening diagnosis results;

- 5. Lower cost: lower cost for detector and ownership, more efficient diagnosis and treatment.

Countries: The Netherlands, Sweden

#### Partners:

| The Netherlands | Sigmascreening,<br>Teledyne DALSA |

|-----------------|-----------------------------------|

| Sweden          | Scint-X                           |

Expected start date: 01-01 2015 Expected end date: 31-12-2017

#### CATRENE Call 7 technology focus: 3D-ICS Projects

The three following projects of the 7th Call belong to the same topics: "3D-ICs". Figure 2 illustrates their respective area and the relationship between them. The on-going project Master-3D has been added to emphasise the coherence of the CATRENE projects related to 3D-ICs.

Brief description: More than Moore (MtM) technologies, three-dimensional (3D) high density technologies, and Systemin-Package (SiP) technologies are prerequisites for compact system integration, which is needed for smart city applications. These compact systems require a mix of many new interconnect technologies such as through silicon via (TSV), through encapsulant via (TEV), redistribution layers (RDL), or micro-bumps, as well as encapsulation technologies, substrates, leadframes and a mix of many different materials. For such complex SiPs expensive prototypes cannot be fabricated without a proper design and simulation environment for extensive premanufacturing simulations (e.g. for design rule

#### Figure 2: Links between CATRENE on-going and forthcoming 7th Call projects related to 3D-ICs

#### 3.1.6. Project CAT601 SiPoB-3D

Co-Design for System-in-Package-on-Board: Managing Complexity and Diversity to Create Novel 3DCompact Systems

#### Project leader: Klaus Pressel (Infineon Technologies)

checks, thermal, electrical). The risk of failing is too high. Thus, a coherent chip-packageboard co-design environment needs to be setup that covers chips and passives, package and the board. SiPoB-3D aims at building up a next level of design methodology for 3D integrated systems, which includes not only the chip and package, but also the board domain.

The consortium will investigate a methodology for mapping the best technology available in companies to design the optimum SiPoB-3D device faster, better and more economic. We must avoid expensive "try and error" loops (time consuming hardware iterations). For design of a compact system, the physics behind the technologies and materials of a compact SiPoB-3D device must be understood. Therefore, emphasize will be put on hardware assessment based on advanced technologies. SiPoB-3D is a holistic approach, which includes investigation and simulation of models that enter into a design library, the design methodology considering multi-physics, and the capabilities setting-up an optimum system as a whole. Data transfer between the different domains needs to be investigated and optimized, especially between the board suppliers and packaged chip suppliers. A global optimum, on chip, package and also on board level needs to be achieved. SiPoB-3D intends to exploit the CoSiP backbone to enable chip/package and board (PCB) co-design for footprints and connectivity. New SiP design rules and checks are a must and will be integrated in the design environment.

A world leading consortium has been set-up. The two European semiconductor suppliers, Infineon Technologies and STMicroelectronics, both with major production in Europe, will collaborate with Continental and Symeo, which both will work on a subsystem on board development, the EDA vendors Atrenta, Docea Power, and CST, and the three small companies Hofmann LP, Schöller-Electronics, and Hitex, the latter three represent the interface to the board (PCB). These partners are supported by four leading European research institutes. The results of SiPoB-3D will allow shorter time to market and support Europe for managing the complexity and diversity for setting up compact 3D systems as a whole including chip, package, and the board.

Countries: France, Germany

#### Partners:

| France  | Atrenta,<br>CEA,<br>Docea Power,<br>STMicroelectronics Crolles,<br>STMicroelectronics Grenoble,<br>Université de Savoie                                                                              |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Germany | Continental Automotive,<br>CST,<br>FAU Erlangen-Nuremberg,<br>Fraunhofer IIS/EAS,<br>Hitex Development Tools,<br>Infineon Technologies,<br>Schoeller-Electronics,<br>Symeo,<br>Hofmann Leiterplatten |

Expected start date: 01-04-2015 Expected end date: 31-03-2018

#### 3.1.7. Project CAT801 TSV-HANDY

TSV HANDY Hvm AND Yield optimisation

### Project leader: Guilhem Delpu (RECIF Technologies)

Brief description:

TSV (Through Silicon Via) is a "More-than-Moore" technology that enables new chip architectures. Some challenges reside along the several steps of process to make TSV products cost efficient. The project aims at supporting the HVM ramp-up and improving the yield for manufacturing TSV products.

The project addresses 4 main challenges:

- 1. The handling of heterogeneous 300mm wafers with edge trim inspection. In fact, on a 3D TSV line, wafers can present highly different mechanical behaviours and physical properties. RECIF targets the development of a 300mm wafer handling platform, which supports as many types of wafer as possible, without having to reconfigure the equipment or swap dedicated modules (like the end effector). This will help end users gaining in equipment flexibility and "up time", because the current solutions on the market have proven not being stable enough. The resulting platform will allow a usage either as a wafer sorter by end users (like NANIUM), or as an EFEM for integration by OEM's (like FOGALE).

- 2. The development of metrology and new logistical concepts for ultra-thin wafers after they are debonded on 380mm frames The manual handling of cassettes and wafer frames is an important contributor to wafer cracks, and open cassettes will become incompatible with the cleanliness requirement, driven by the shrinking of the pitch for micro-bumps (down to 20µm). There is a need to bring "Front End" methods and best practices, to "Middle End" (TSV lines). But 300mm modules and automation equipment are not compatible to handle 380mm film frames, because of their dimensions. For instance, a 300mm load port cannot handle 380mm substrates due to mechanical interferences. However, a solution is to consider re-using some of the 450mm modules that have been designed already (cf: CATRENE and ENIAC JU 450mm projects), and adapt it to the need of 380mm film frames. This way, industry will take benefit from existing standardized interfaces, with dimensions that are compliant with substrates wider

than 300mm, up to 450mm. ENTEGRIS and RECIF have designed 450mm modules which can be adapted to support the handling of film frames, within a cleaner and highly automated environment. ENTEGRIS 450mm carrier with 380mm insert for frames will be handled by RECIF 450mm handling platform. ENTEGRIS will develop new carriers to be compatible with higher level of automation, and the partners will demonstrate the industrial relevance of tracking the wafers debonded on frames thanks to RF tags integrated into the frame, at substrate level.

3. The investigations for the FO-WLP process, for round wafers larger than 300mm The project will investigate the manufacturing of surfaces larger than 300mm in Fan-Out Wafer Level Packaging for advanced packaging. In fact, since in this process, the size of the reconstituted mold wafer is independent of the original incoming silicon, GaAs or SiGe wafer, processing larger panels drives the cost per die down. Therefore, current 300mm wafer diameter for Fan-Out WLP needs to be enlarged (batch processing of large panel) and 330mm reconstituted wafer for Fan-Out WLP/eWLB and 450mm Si wafer for Fan-In WLP/WLCSP and Fan-Out WLP/eWLB, need to be studied and considered as next steps to be implemented in high volume manufacturing environment.

4. <u>The improvement of temporary</u> <u>bonding and debonding processes</u>, The work on temporary bonding consist in integrating the coating and bonding capability for "novel adhesives solutions" in order to increase the throughput and the performance of the temporary bonding process. On the debonding side, the project will evaluate the debonding process with wafers bonded with this new process and implement the new standardization rule developed in the project (re-using 450mm automation modules like carriers and handling platform).

Synergies will be created with other CATRENE projects like NGC450, SOI450, MASTER\_3D andwith the ENIAC JU EEM450PR project. The industrial partners intend to release new products to the market by early 2018.

Countries: Austria, Belgium, France, Germany, Portugal

#### Partners:

| Austria  | EV Group E. Thallner                                                               |  |  |

|----------|------------------------------------------------------------------------------------|--|--|

| Belgium  | Imec                                                                               |  |  |

| France   | CEA-LETI,<br>Fogale Nanotech,<br>RECIF Technologies,<br>STMicroelectronics Crolles |  |  |

| Germany  | ENTEGRIS                                                                           |  |  |

| Portugal | NANIUM                                                                             |  |  |

Expected start date: 01-04-2015 Expected end date: 31-03-2018

#### 3.1.8. Project CAT802 SAM3

Smart Analysis Methods for 3D Integration in Advanced Microsystems and Corresponding Materials

Project leader: Klaus Pressel (Infineon Technologies)

#### Brief description:

More-than-Moore (MtM), System-in-Package (SiP), as well as 3D high-density integration technologies are a prerequisite for enabling the design of compact microelectronic devices and are enablers for European technology leadership. With increasing integration density the impact of right material choices is becoming of outstanding importance (e.g. electrical data, stress, adhesion, CTE matching). During the last decade all package materials have been changed, which is a consequence of miniaturisation as well as integration of more functionality into smaller volume. We expect that this trend in assembly and packaging will proceed (see discussions in ITRS roadmap, iNEMI roadmap, as well as international conferences). Increased functional density and small foot-print of innovative systems are achieved by innovative interconnects, such as Through Encapsulant Via (TEV), Through Silicon Vias (TSV) and redistribution layers applied to advanced assembly and packaging technologies. Examples of such advanced packaging technologies are chip embedding in mold materials (eWLB), chip embedding in laminate materials as well as 3D stacking.

For these new and complex devices, failure analysis becomes a more and more expensive part of product development. An advanced failure analysis strongly supports to meet the right timing for product introduction, a fact that provides an outstanding saving potential for companies. New materials and processes must be developed and qualified requiring effective analysis techniques to understand new failure modes and reliability limiting factors caused by thermo-mechanical mismatch, residual stresses and interaction of new materials and processes. Thus, for development of complex heterogeneous SiP devices and for reaching required reliability, innovations in failure diagnostic and material analysis are required and must be aligned to the SiP technology developments in effective failure analysis workflows.

In particular, the existing failure analysis techniques are limited in localizing electrical defects in these compact SiP devices with multilevel wiring. Efficient and artefact free sample preparation to apply physical analysis techniques are limited. Techniques to determine local residual stresses and material parameter within the package are required for reliability modelling. The four major European semiconductor and system suppliers Infineon, STMicroelectronics, Bosch and Thales will collaborate with eleven equipment and analytical method suppliers from Germany and France. The work is supported by five academic institute partners. The SAM3 project will improve the capability of the semiconductor and system suppliers (Infineon, STMicroelectronics, Bosch, and Thales) to avoid defects and failures during product development based on better material understanding. Comprehensive, well adapted and effective failure analysis work flows provide essential support for technology development, process and product qualification, and quality/process control during fabrication. The project results will provide inputs for advanced simulation approaches or reliability models that can be used to identify and consider reliability problems already during the product development phase ("design for reliability"). Such concepts gain increasing importance since they allow to reduce time-to-market and development cost. In addition proper analysis work flows allow reliability assessments to achieve short-time to market readiness, proven application potential, and future customer acceptance of innovative MtM, SiP and 3D integration solutions. Besides, the SAM3 project will allow the equipment suppliers to better understand the needs of the semiconductor and system suppliers and tune their roadmaps according to the need of the industry with worldwide market perspectives.

Countries: France, Germany

#### Partners:

|       | CNRS-AMU-LP3,               |

|-------|-----------------------------|

|       | DIGIT CONCEPT,              |

|       | GREMAN (UMR 7347),          |

| rance | ORSAY-PHYSICS,              |

|       | STMicroelectronics Tours,   |

|       | STMicroelectronics Rousset, |

|       | STMicroelectronics          |

|       |                             |

#### CATRENE Programme Review - Year 2014

| Sermany | 3D-Micromac,<br>Fraunhofer Institute for Mechanics of<br>Materials,<br>Infineon Technologies,<br>Muegge,<br>Nanoworld Services,<br>point electronic,<br>PVA TePla Analytical Systems,<br>Reutlingen University,<br>Robert Bosch,<br>SmarAct,<br>WITec |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

Expected start date: 01-03-2015 Expected end date: 28-02-2018

#### 3.2. Projects ended in 2014

#### 3.2.1. Overview Table

| Call # | Project<br>Number | Acronym     | Work Area                              |

|--------|-------------------|-------------|----------------------------------------|

| 1      | CA303             | OPTIMISE    | Automotive and Transport               |

| 2      | CA402             | THOR        | Health and the Ageing Society          |

| 3      | CA308             | ICAF        | Automotive and Transport               |

| 3      | CA403             | RELY        | Health and the Ageing Society          |

| 3      | СТ206             | Reaching22  | Semiconductor Process and Integration  |

| 3      | СТ305             | SOI450      | Equipment, Materials and Manufacturing |

| 3      | СТ306             | NGC450      | Equipment, Materials and Manufacturing |

| 3      | CT402             | 9D-Sense    | Semiconductor Process and Integration  |

| 4      | CT210             | Dynamic-ULP | Semiconductor Process and Integration  |

#### 3.2.2. Project CA303 OPTIMISE

Optimisation of Mitigations for Soft, firm and hard Errors

#### Project leader: Florent Miller (EADS)

#### Brief description:

The reliability of electronic components is an essential element for automotive power electronic, avionic and space applications. However, commercially available submicron technologies are inherently sensitive to the incidence of energetic particles due to the low voltages at which they work (3,3, 2,5, 1.8 V....) and due to their very small node size. As example, the high sensitivity of the advanced technologies (below 90nm and down to 28nm) was assessed

experimentally in the project and the associated risk for applications at ground and airplane levels was quantified with a potential increase in the error rate reaching almost +50% on 28nm technologies.

Starting from this statement, OPTIMISE project followed two main goals, applied to three different applications automotive power electronic, avionic-FPGA and space ASICs:

<u>Acquire knowledge</u> on new radiation threats that may impact future electronic equipment and work in close collaboration with standardization bodies to propose guidelines or standards to be able to perform relevant risk assessment;  <u>Develop and validate mitigation techniques</u> from layout to application architecture levels.

The first step towards the realisation of these two objectives was the development of tools for the radiation sensitivity assessment. In the following of the PARACHUTE project (MEDEA frame), the relevancy of using laser and emulation platforms to study the radiation sensitivity has been pursued on a wide variety of devices (SRAM, test vehicles, SRAM based FPGA, ...). In addition, the first experiments in the world demonstrating the possibility to simulate destructive failures using laser in Wide Band Gap power devices have been successfully performed by IMS and EADS allowing achieving one of the first detailed study of the radiation induced failures in SiC power devices.

Automotive application

#### Acquire knowledge

An important highlight is the standardized method proposed by Renault regarding reliability assessment due to radiation effects on power components.

#### Mitigations development & new products

- CNM designed an IGBT with an internal current sensing. it has been demonstrated the possibility to measure a SEL (Single Event Latchup through the sense electrode, without impact on main circuit, paving the way to possible early detection of destructive event, especially in the case of slow power electronics devices.

- STM Tours has been able to develop a new SiC diode technology and will propose a full range of SiC 1200V diodes in 2014 benefiting of improvements on radiation tolerance.

#### Avionic application

#### Acquire knowledge

Airbus proposed inputs for the update of the radiation test standards for avionics.

#### Mitigations development & new products

An Avionic I/O board implemented in a Stratix IV FPGA has then been tested using a fault injection platform:

- A state of the art DRAM fault-tolerant controller developed and patented by EADS was enhanced to support the more advanced DDR3 memory type used in the system.

- The CPU Checker IP was developed to detect errors enabling a continuous observation of the microprocessor execution without disturbing it.

- A selective mitigation approach developed by TIMA focuses on error detection in the FPGA Look-Up Table (LUT) configurations taking advantage of unused FPGAs resources.

#### SPACE ASIC

#### Acquire knowledge

On the standards side RIIF initiative has been launched.

#### Mitigations development & new products

- UC3M developed the AMUSE tool able to classify the cells of a circuit with respect to Single Event Effects (SEE).

- Arquimea synthesized a SEL free ASIC with a hardened 90nm CMOS library developed during the project by ATMEL. The measures of SETs width have shown an improved SET robustness of the hardened library compared to 90nm commercial cells (ratio around 100). The radiation assessment of

the 8T SRAM cells has been performed by UIB.

In order to improve the design of robust circuits, iRoC and TIMA developed three innovative Radiation Hardening by Design (RHBD) solutions. These techniques have been used to design three hardened versions of the LEON2 processor synthesized using the ATMEL's hardened library. These hardening techniques have been assessed by performing fault injection simulations and have been validated by iRoC and TIMA. Finally, these hardening techniques have been completed by the CPU checker proposed by UC3M in the avionic chain value and ported by UC3M and iRoC into the three hardened LEON2 design. These mitigation techniques were implemented in the test vehicle V53, which was manufactured at the end of May 2014 and tested under heavy ion in June 2014. The SEE results of the LEON2 circuits have shown a very good SET coverage protection with a benefit on the silicon area, and power overhead, without degrading the performances. On the exploitation side, this hardened library is used to develop a new ATMEL spacegualified SPARC processor that will address the space market.

#### Countries: France, Spain

#### Partners:

|        | Airbus Defense and Space,  |

|--------|----------------------------|

|        | ATMEL NANTES,              |

|        | CEA,                       |

|        | Continental Automotive,    |

|        | EADS Innovation Works,     |

| France | IMS Lab,                   |

| France | iRoC Technologies,         |

|        | RENAULT,                   |

|        | STMicroelectronics,        |

|        | TIMA,                      |

|        | Universite Provence IM2NP, |

|        | Valeo Interior Controls    |

Alter Technology Group, Arquimea Ingenieria, CNM-Centro Nacional de Microelectronica IMB, D&T Microelectronica, Thales Alenia Space, UIB-University of Balearic Islands, Universidad Carlos III Madrid

Start date: 01-01-2015 End date: 31-12-2017

Spain

#### 3.2.3. Project CA402 THOR

Striking technologies for Power

Project leader: Mark van Helvoort (Philips Healthcare)

Brief description:

The THOR Project, coordinated by Philips Healthcare, has delivered solutions for packaging, cooling and electromagnetic compatibility. This helps industry to transform the Silicon Carbide (SiC) market from a device to a power modules business. This transformation will lead to a jump in growth of the SiC device market from 26% to 39% within the next year according to Yole Development.

In modern power converters, most of the volume is occupied by cooling components and electrical filters. SiC based power devices reduce both the requirements on cooling and filtering. THOR has exploited this aspect by developing high temperature packaging, compact cooling systems and smaller filters. Compact power conversion systems with a very high power density have been demonstrated in three application areas: aeronautics, automotive and healthcare.

These compact and highly efficient converters are essential for addressing the environmental challenges in terms of  $CO_2$  emission and over reliance on fossil fuels. Power converters will significantly reduce the weight of cabling in a single aircraft thus diminishing fuel consumption with an additional 30% being saved by storing transient energy during braking. In the medical area, more compact systems at a lower cost helps to address the health challenges in the ageing society.

Key to the success of the THOR project was its coverage of the full supply chain from semiconductor device level to power system integrator in combination with three application areas to leverage the economy of scale. The commercial advantage is a stronger competitive situation for the different industrial partners, because recent advancements in power electronics technology provided by the academic partners have been integrated into advanced applications. This ranges from SiC and Sol technology to full compact power converters integrated in large systems.

Such broad coverage was made possible by the unique support of two large European support programmes: CATRENE and EURIPIDES<sup>2</sup>. The information sharing and cross-fertilization within the THOR consortium was excellent; more than 70 reports with results have been internally exchanged and new, long-lasting, collaborations have been established. Furthermore, the key players within THOR guaranteed efficient cooperation with other related European projects.

THOR also shared its newly generated knowledge amongst the academic and industrial public. More than 30 papers have been written, 25 presentations were given and 12 patent applications have been submitted. A book on EMC of large systems and installations has also been published in Dutch and is currently being translated.

The first products based on THOR technology are already available on the market. In September 2012, STMicroelectronics released their SiC diodes for photovoltaic converters. They will extend their range this year to ad-

42

ditional applications and SiC Mosfets will follow soon. Soitec and NXP have a new silicon-on-insulator process in place facilitating the design of high temperature drivers and the integration of low-voltage and high-voltage integration at lower cost.

For electric vehicles, Valeo has demonstrated a compact air-cooled high-voltage DC/DCconverter with efficiency 93% and 95% over a very broad output power range. The vapour chamber and heat sink have been designed such that the cooling capabilities of the converter are independent of the mounting orientation, thus offering large flexibility to car designers.

Labinal Power Systems, Airbus Group Innovations, Thales Microelectronics and CIRTEM have demonstrated a compact power converter, which covers a very large temperature range such that it can be located at both aeronautic engines and in brakes on airplanes (very high temperatures).

Philips Healthcare and the Dutch SME Prodrive demonstrated the capabilities of full digital control for power electronics. Among others, a compact high voltage power supply was shown with an ideal topology for introducing SiC components. Pilot tests in hospitals are already ongoing. Further, a feedback system was developed, which can correct up to 10 dB variations in amplifier gain.

Countries: Belgium, France, The Netherlands

#### Partners:

| Belgium | NXP Semiconductors                                                                                                                                                                                                                                                                  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| France  | Airbus Group Innovations,<br>Ampère Insa Lyon,<br>Cirtem,<br>Epsilon Ingénierie,<br>Labinal Power Systems (Safran),<br>Soitec,<br>ST Microelectronics,<br>Thales Microelectronics,<br>University de Versailles-Saint-Quentin-en-<br>Yvelines,<br>Valeo Systèmes de Contrôles Moteur |

| The Netherlands | Bruco Integrated Circuits,<br>NXP Semiconductors,<br>Philips Healthcare,<br>Prodrive,<br>TUE-Technical University Eindhoven |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------|

|-----------------|-----------------------------------------------------------------------------------------------------------------------------|

Start date: 01-10-2010 End date: 31-03-2014

#### 3.2.4. Project CA308 ICAF

#### Image Capture of the Future

#### Project leader: Jochem Herrmann (Adimec)

#### Brief description:

ICAF project developed and researched hardware and processing algorithms for single lens 3D camera systems, multi view camera systems, broadcast video over internet protocol systems and high speed vision cameras for 3D applications. The project delivered 3D single lens microstereopsis camera, multi view systems, depth from luminance, depth image based rendering, super resolution of depth maps and denoising and demosaicing for super slow motion HD cameras (including IP based transmission). In particular the project delivered the first 3D single lens stereopsis camera and the first HDTV slow motion camera beyond triple speed that can continuously output a slow motion stream together with a normal HDTV stream. In addition the project provided high data rate transmission ICs to extend the worldwide CoaXPress standard with new protocols and higher bit rates up to 12.5 Gbps.

The products that incorporate results of the ICAF project are professional broadcast cameras, cameras for machine vision, the global security and medical markets, CoaXPress transmission ICs, CMOS image sensors and compression IP. These products are manufactured within Europe and shipped worldwide. The exploitation results and expected market impact by partners are:

- Adimec has the first commercial camera with 2 Gpix/s continuous data rate streaming capability and the first rugged surveillance camera with CoaXPress;

- Axon has won 5 awards with his implementation and definition of the new Video over IP standards SMPTE2022 and AVB:

- EqcoLogic introduced its next-gen CoaXPress transceiver solutions. First engineering samples have been sent to selected customers for evaluation;

- Grass Valley has introduced a very successful 6x slow motion HDTV camera. They won 3 awards with this camera;

- Grass Valley has patented the principle used in the single lens microstereopsis camera;

- IntoPix has strengthened its position in video compression with first J2K Video over IP reference FPGA design;

- On-Semi has Strengthening its position in state of the art high speed and industrial imaging;