# An open European Nanoelectronics Infrastructure for Innovation

# Bridging the gap between risk-taking research and innovative technological solutions

# **Final Report**

March 2014

# Table of Contents

| Core Group                                                                |    |

|---------------------------------------------------------------------------|----|

| Foreword                                                                  |    |

| 1. Executive summary                                                      | 6  |

| 1.1 Context                                                               |    |

| 1.2 Objectives                                                            |    |

| 1.3 Methodology                                                           |    |

| 1.3.1 Selection of the R&D nanoelectronics programmes                     |    |

| 1.3.2 Working group                                                       |    |

| 1.3.3 Workshops                                                           |    |

| 1.3.4 Template                                                            |    |

| 2. Technological roadmaps                                                 |    |

| 2.1 Nanoscale FET                                                         |    |

| 2.1.1 Applications needs                                                  |    |

| 2.1.2 Current position                                                    |    |

| 2.1.3 Future vision                                                       |    |

| 2.1.4 Areas of Cooperation                                                |    |

| 2.1.5 Roadmaps                                                            |    |

| 2.2 Smart Energy                                                          | 21 |

| 2.2.1 Applications needs                                                  |    |

| 2.2.2 Current position                                                    | 23 |

| 2.2.3 Future vision                                                       | 24 |

| 2.2.4 Areas of Cooperation                                                |    |

| 2.2.5 Roadmaps                                                            |    |

| 2.3 Smart Sensors                                                         |    |

| 2.3.1 Applications needs                                                  |    |

| 2.3.2 Current position                                                    |    |

| 2.3.3 Future vision                                                       |    |

| 2.3.4 Areas of Cooperation<br>2.3.5 Towards Roadmaps-Proposed methodology |    |

|                                                                           |    |

| 3. Heterogeneous Integration                                              |    |

| 3.1 Applications needs                                                    |    |

| 3.3 Future vision                                                         |    |

| 3.4 Areas for cooperation                                                 |    |

| 3.5 Roadmaps                                                              |    |

| 4. System integration                                                     |    |

| 4.1 Applications needs                                                    |    |

| 4.2. Current position                                                     |    |

| 4.3 Future vision                                                         |    |

| 4.4 Areas of cooperation                                                  |    |

| 5. Manufacturing science                                                  |    |

| 5.1 Current position                                                      |    |

| 5.2 Future vision                                                         |    |

| 5.3 Areas of cooperation                                                  |    |

| 6. Ecosystems-Research Infrastructure                                     |    |

| 6.1 Definition                                                            |    |

| 6.2 Structuration                                  |    |

|----------------------------------------------------|----|

| 6.3 Ecosystems                                     |    |

| 6.4 Excellence Centers                             |    |

| 6.5 Mechanisms of collaboration                    |    |

| 6.6 Routes of access                               | 51 |

| 7. Impact                                          | 51 |

| 8. Long-term strategic Programs                    | 53 |

| Annexes                                            | 54 |

| 1) Expression of interest forms                    | 54 |

| 2) Key Workshops                                   |    |

| 3) Identification of research facilities (Example) |    |

| 4) Follow-up activities                            |    |

| 5) References                                      |    |

|                                                    |    |

No single Member State has the multi-disciplinary capability to address and sustain the Research & Development & Innovation needed to cover the full value chain and no single company can master all the advanced micro and nanoelectronics technologies necessary to remain competitive. The ENI2 initiative will contribute to structure and coordinate R&D&I in Europe and thereby address fragmentation, avoid unnecessary duplication of effort identify and encourage new or hitherto uncovered areas of technology development and build upon existing and emerging clusters to create a European eco-system 'at the service' of European industry.

> ENI2 Core Group May 2011

# **ENI2 CORE GROUP**

| Participant organization name                                        | Country         |

|----------------------------------------------------------------------|-----------------|

| INSTITUT POLYTECHNIQUE DE GRENOBLE                                   | FRANCE          |

| CONSORZIO NAZIONALE INTERUNIVERSITARIO PER LA NANOELETTRONICA        | ITALY           |

| COMMISSARIAT A L ENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES       | FRANCE          |

| ASM INTERNATIONAL N.V.                                               | THE NETHERLANDS |

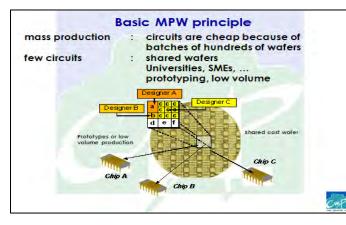

| CIRCUITS MULTI-PROJETS                                               | FRANCE          |

| FRAUNHOFER-GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG E.V | GERMANY         |

| INTERUNIVERSITAIR MICRO-ELECTRONICA CENTRUM VZW                      | BELGIUM         |

| AIT AUSTRIAN INSTITUTE OF TECHNOLOGY GMBH                            | AUSTRIA         |

| AGENCIA ESTATAL CONSEJO SUPERIOR DE INVESTIGACIONES CIENTIFICAS      | SPAIN           |

| ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE                             | SWITZERLAND     |

| EDACENTRUM GMBH                                                      | GERMANY         |

| FORSCHUNGSZENTRUM JUELICH GMBH                                       | GERMANY         |

| ION BEAM SERVICES                                                    | FRANCE          |

| CATALAN INSTITUTE OF NANOTECHNOLOGY                                  | SPAIN           |

| INFINEON TECHNOLOGIES AG                                             | GERMANY         |

| INSTYTUT TECHNOLOGII ELEKTRONOWEJ                                    | POLAND          |

| KUNGLIGA TEKNISKA HOEGSKOLAN                                         | SWEEDEN         |

| MICRON SEMICONDUCTOR ITALIA SRL                                      | ITALY           |

| NATIONAL CENTER FOR SCIENTIFIC RESEARCH "DEMOKRITOS"                 | GREECE          |

| NXP SEMICONDUCTORS BELGIUM NV                                        | BELGIUM         |

| OPEN ENGINEERING                                                     | BELGIUM         |

| INSTITUT SINANO ASSOCIATION                                          | FRANCE          |

| STIFTELSEN SINTEF                                                    | NORWAY          |

| STMICROELECTRONICS S.A.                                              | FRANCE          |

| STMICROELECTRONICS SRL                                               | ITALY           |

| THALES SA                                                            | FRANCE          |

| THYIA TEHNOLOGIJE D.O.O                                              | SLOVENIA        |

| TECHNISCHE UNIVERSITEIT DELFT                                        | THE NETHERLANDS |

| NEDERLANDSE ORGANISATIE VOOR TOEGEPAST NATUURWETENSCHAPPELIJK        | THE NETHERLANDS |

| ONDERZOEK - TNO                                                      |                 |

| UNIVERSITY COLLEGE CORK, NATIONAL UNIVERSITY OF IRELAND, CORK        | IRELAND         |

| UNIVERSITE CATHOLIQUE DE LOUVAIN                                     | BELGIUM         |

| UPPSALA UNIVERSITET                                                  | SWEDEN          |

| TEKNOLOGIAN TUTKIMUSKESKUS VTT                                       | FINLAND         |

| TECHNISCHE UNIVERSITEIT EINDHOVEN                                    | THE NETHERLANDS |

| TUBITAK                                                              | TURKEY          |

| INSTITUTO DE TELECOMUNICACOES                                        | PORTUGAL        |

# Foreword

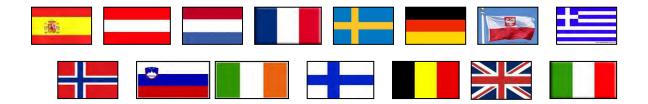

This report is built-up together by all the members of the ENI2 Core Group. The members of the Core Group serve on behalf their organization and have a well-recognized expertise in their respective field and a solid experience in European Collaborative Programmes.

# 1. Executive summary

#### 1.1 Context

The highly-dispersed nature of the nanoelectronics R&D activities in Europe limits the creation of visible effective impact. Europe can be proud to have the global market and manufacturing leaders in advanced CMOS, MEMS, in power semiconductors, security ICs and materials and equipment industry. However, there are no European agglomerations such as Silicon Valley or the Asian foundry companies or well-known economy drivers as kind of global "brand marks" that can act as job creation machines. In nanoelectronics in particular, Europe is suffering from the absence of a global and consistent R&D approach. There is a vital need to identify who the key players are, reinforce alliances between them and organize a new collaborative paradigm to achieve an economic strength based on collimated forces and knowledge. Bundled forces also means, that research based on public funding needs to be more efficient: the research funds used across Europe need to be better coordinated and there needs to be less duplication of work that has no clear justification for being conducted.

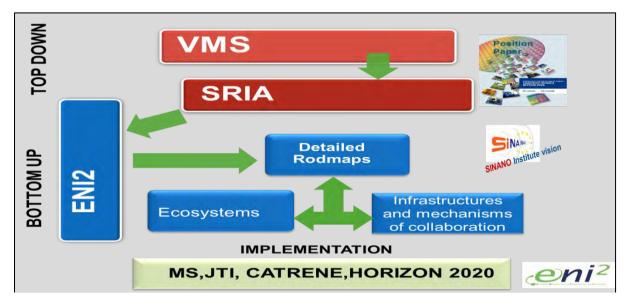

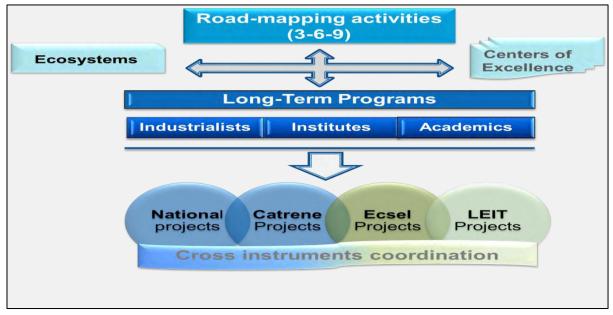

In line with the VMS and the SRIA issued by AENEAS and CATRENE and in the context of Horizon 2020 and of the new JTI, the ambition of **The European Nanoelectronics Infrastructure for Innovation (ENI2)** is designed to create mid- and long- term technology roadmaps for cooperative R&D projects in nanoelectronics.

ENI2 members include academia, research institutes, multinationals and SMEs from 15 European countries. ENI2 will help to optimize the efforts, time and funds spent on R&D projects at international level. This will mainly be done by aligning the technological needs and roadmaps for nanoelectronics between industrial and academic partners within a long-term perspective. The ENI2 initiative will also contribute and enhance the possibilities of exploitation of results obtained by research institutes and universities.

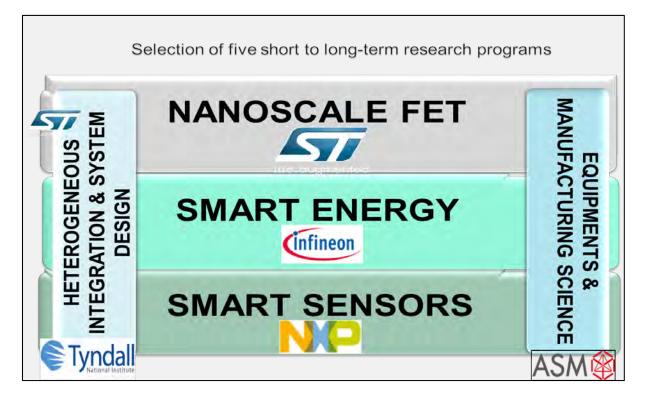

The ENI2 Roadmaps will focus on the following 5 areas:

- Nanoscale FET (Set Top Box, Smartphones, HPC, mini-servers)

- **Smart Energy** (smart grid, electrical cars).

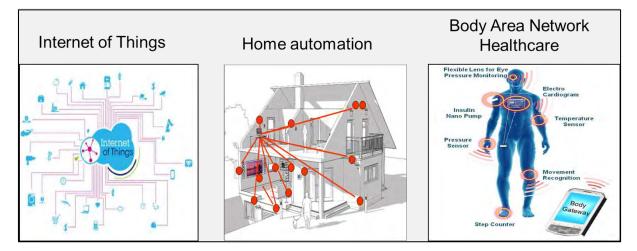

- Smart sensors (Internet of things, e-health).

- **System Design** and **Heterogeneous integration** to offer greater functionality at lower cost.

- Novel semiconductor equipment and manufacturing processes.

## 1.2 Objectives

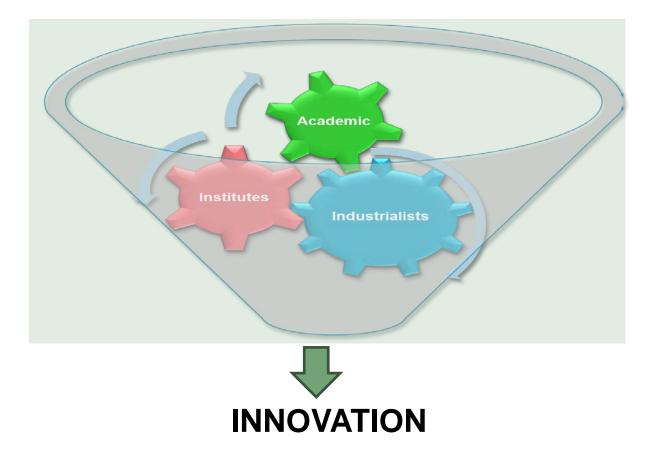

The collaborative innovation poses four major challenges:

- Development of a vision for collaborative innovation based on the detailed content of R&D&I Programs of European interest,

- Ensuring that the partners are ready to collaborate with each other

- Building trust among partners,

- Defining the respective tasks of the members of the ecosystems and the mechanisms for collaboration.

On the other hand, the key factor of a successful collaborative innovation ecosystem will be based upon the possibility to move from the traditional opportunistic and focused topic calls to flexible and transparent procedures, as already partially started in recent years with the JTI's and PPP's. This will support long term funding support and will create a framework able to transform R&D activities into advanced processes and innovative silicon devices to strengthen European research ecosystems and manufacturing in Europe.

The ENI2 initiative started in 2011 with a core group of partners with the ambition to:

- Create the vision

- Build the team

- Define the tasks and individual contribution based on shared understanding of European technology challenges

- Drive the execution

- Install the culture

- Propose long term Programs

**In May 2011 the core group of academic, institutes, and industry experts has issued a position paper with a shared vision,** consolidated during sessions in Paris and Brussels. The tasks and individual contributions have been defined in January 2012

and reviewed during several Workshops. To drive the execution and install the culture a working Group, ENI2 has been embedded in AENEAS with the following management structure:

| Role               | Company                                                                        | Name                                                                                             |  |

|--------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|

| Project Manager    | ST                                                                             | G.Casanova                                                                                       |  |

| Steering Committee | Sinano-Tyndall-FHG-<br>NXP-IFX-ST-IMEC-<br>ITE                                 | F.Balestra-A.Mathewson-J.Pelka-<br>P.Grabiec-W.Dettmann -P.Pype -<br>G.Casanova -A.Van den Bosch |  |

| Project Team       | Core Group                                                                     | Annexe                                                                                           |  |

| Team Leads         | TUDelft-STE-Thales-<br>TUE-ST-NXP-IFX-<br>Sinano-FHG-KTH-<br>CMP-Tyndall-IMEC- | G.Thomas-M.Ostling -A.Bouffic<br>-F.Balestra - J.Pelka- B.Courto                                 |  |

| Executive Sponsors | Aeneas office                                                                  | M.Annergan                                                                                       |  |

Based on the outcomes and assessment of ENI2 acquired during the preliminary phase, it was agreed to focus the work on the:

**1)** *Definition of a strong set of common long term R&D strategic nanoelectronics programs* that will stimulate innovation in Europe.

2) Establishment of strategic groupings of research communities with common *interests* and expertise which will lead to innovation oriented R&D programmes and focus resources on target issues.

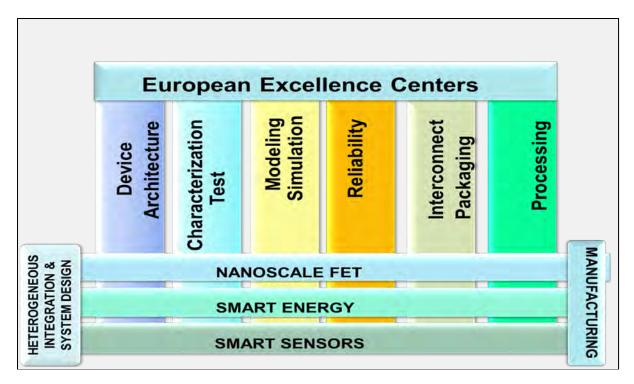

*3) Definition of the infrastructures and the associate collaborative mechanisms* including the:

- Structuration of the three levels of the research infrastructure

- Interaction and mechanisms of the collaboration between the three levels

- Definition of European Excellence Centers

- Routes of access for SMEs and Universities to the ENI2 technologies capabilities.

## 1.3 Methodology

#### 1.3.1 Selection of the R&D nanoelectronics programmes

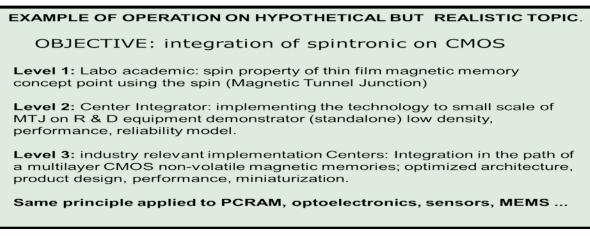

Five domains have been identified, which cover the need in Europe for manufacturing specialization and product competitiveness in advanced applications, namely **NANOSCALE FET**", **"SMART ENERGY"**, **"SMART SENSORS"**, **SYSTEM INTEGRATION & HETEROGENEOUS INTEGRATION, MANUFACTURING & SCIENCE**. Within each domain we have identified key projects and research lines based on "short", "medium" and "long" term perspectives.

The rationale behind this concept is that the European Ecosystem must develop a clear vision of the technological priorities to be pursued for each domain and within the different timeframes. For each technological domain, the outcomes will result in the definition of "short-term-projects" (technological development), led by Industrial Partners with Research Institutes and Academia playing a support role, "medium-term-projects" led by Research Institutes with Industry and Academia playing the role of enduser and scientific consultants, respectively, and finally "long-term-projects" led by Academia where Research Institutes and Industry have the role of advisor/steering partners.

#### 1.3.2 Working group

For each of the technological domains, one ENI2 partner is responsible for promoting open discussion among partners around the different topics related to the domain, classifying them within the three time horizons, with the goal to converge on priorities as well as identifying and elaborating *projects*. For the technological domains that have been defined as the main pillars in order to sustain European development in the nanoelectronics area, the objective was to define, map and select the different topics as well as the priorities for the different time horizons (3, 6, 9 years). On Heterogeneous Integration, the objective of the working group (WG) was to place specific attention on the definition of the collaborative activities that will bring added value at European level and, which will contribute to making heterogeneous integration a reality. Concerning the infrastructure domain, the mechanisms associated with the collaboration between the partners and the routes to access of the ENI2 technologies have been identified as the key issue to make the collaboration effective.

#### 1.3.3 Workshops

Several Workshops with many European laboratories have been organized and thorough discussions have been undertaken with the principal players on the European nanoelectronics stage; from academia, to pre-industrial centers up to industry; in order to establish the major structural and technical challenges that face the European nanoelectronics community.

#### 1.3.4 Template

In order to gather all relevant information on R&D priorities as well as the specific expertise resident in each location, the template shown below (e.g. Nanoscale FET) have been filled in by each ENI2 member. This template has also been used for the work devoted to Ecosystem and Research Infrastructures (see Annex).

| ENI2 Expression of Interest form                           |                                     |                       |  |

|------------------------------------------------------------|-------------------------------------|-----------------------|--|

| Nanoscale FET<br>Areas of collaboration                    | Potential<br>contribution<br>Yes/no | Priority<br>level (*) |  |

| Properties of materials and devices built at the nanoscale |                                     |                       |  |

| Modeling of properties of materials and devices            |                                     |                       |  |

| Multi-physics and multi-scale modeling methodologies       |                                     |                       |  |

| Novel materials and new functionalities                    |                                     |                       |  |

| New device architectures                                   |                                     |                       |  |

| Novel interconnects architectures                          |                                     |                       |  |

| Development of ultimate processing technologies            |                                     |                       |  |

| Nano devices for adding new functionalities to CMOS        |                                     |                       |  |

| Physical and electrical nano characterization              |                                     |                       |  |

| Integration of very high densities of nano devices         |                                     |                       |  |

|                                                            |                                     |                       |  |

|                                                            |                                     |                       |  |

| Other suggested collaboration areas                        |                                     |                       |  |

|                                                            |                                     |                       |  |

# 2. Technological roadmaps

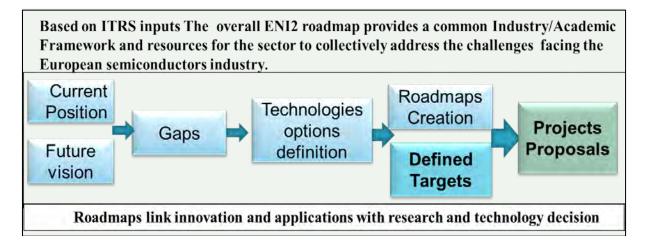

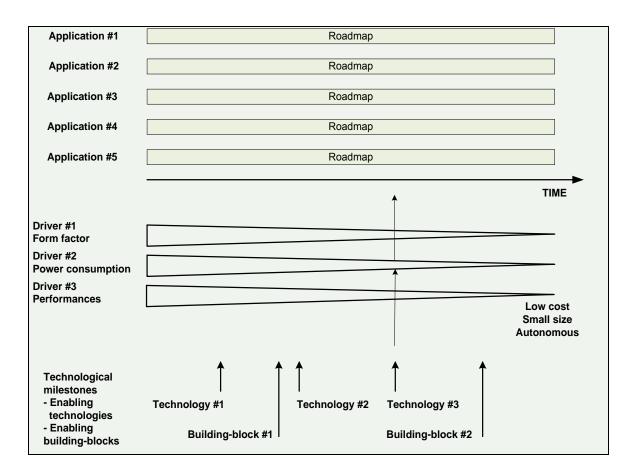

The ENI2 Technology road mapping as presented in this report has to be perceived as an effective tool for technology planning and the coordination of efforts at the European level. By capitalizing on the ITRS, the ENI2 road mapping process provides a consolidated and structured consensus view of the future S&T landscape at European level available to decision makers. This technology road mapping has been based on joint, detailed and shared collaborative R&D. The main benefit that it produces is that it identifies the R&D paths to make better technology investment decisions. It does this by identifying critical technologies and technology gaps as well as identifying ways to leverage R&D investments and accelerate the time to market. **This kind of technology road mapping is particularly relevant when different technology options for meeting certain performance objectives need to be pursued**. If there is high uncertainty or risk, different R&D paths may be pursued concurrently. The roadmap identifies precise objectives and helps to focus resources on the critical technologies that are needed to meet those objectives. This focusing is important because it allows the use of R&D resources in the most efficient way. **For the technological domains**

# (nanoscale FET, Smart energy and Smart sensors), we have agreed on the following roadmapping process:

- Identify the "Applications" that will be the focus of the roadmap.

- Describe the state of the art and the vision.

- Define the technology options and select the areas of cooperation to be addressed at -European level

- Create the roadmaps by specifying the major technology areas (devices,

interconnect, materials.....) and associated targets

- Generate and implement a plan to develop and deploy Long term Programmes.

The figure below illustrates the approach to be taken:

# 2.1 Nanoscale FET

This domain of the electronic industry is essentially the one that is related to digital technologies (micro components, memories and logic circuits). These devices benefit greatly from a continuous increase in integration density to become obviously smaller but also faster and cheaper. This trend has been developing without abatement for the last 30 years mainly thanks to the MOSFET. CMOS technology is also used for analog chips and for communications chips. However, in this case the MOSFETs are complemented by other active (LDMOS, HBTs...) or passive devices to create the mixed signal class of chip possible. For some time, there has been a consensus that the scaling will end (due to economic or physical reasons) and that BEYOND CMOS devices need to be studied in order to keep working on the reduction of energy consumption of the electronic functions. For memory devices, whose weight in all ICT applications has become increasingly important, the end of the conventional scaling roadmap seems to have already been reached. New architectures and storage mechanisms have to be introduced to satisfy increasing requirements in terms of storage capacity, access speed and low power. With increased transistor density, we have moved from Microelectronics to Nanoelectronics but we are facing a power crisis (especially in battery powered electronics) and power efficiency will become the new Figure of Merit (FoM) for the electronics industry. On the basis of this kind of issue, Nanoelectronics will soon morph into Femtojoule electronics where a stronger emphasis will be placed on power reduction rather than geometry scaling.

#### 2.1.1 Applications needs

The digital IC market based on CMOS technology is evolving from being computercentric to being focused on mobile platforms. Key application segments in the past were first large computers, then personal computers, which became common in the early 1980s; this phase continued for almost 30 years up until 2009/2010. While personal computers will continue to have volumes of 300M units per year; smart phones have become the next key platform. This trend will be strengthened by the complementary tablet computer, which is a bridge between smart phones and notebook computers. The new multimedia mobile platform volumes will reach 1.5B units in 2015 and will be the most important platform target for IC vendors. The key semiconductor challenge has moved from only performance, to energy efficiency and extreme miniaturisation due to portability and long battery lifetime requirements of mobile computing. One of the main requirements of these systems is the availability of a large storage capability for high quality images, music and videos, based on solid state nonvolatile memories. Until now the needs have been satisfied by a combination of DRAM and high density NAND Flash devices, but power constraints are affecting the former, and the latter are close to their scaling limits. We need to develop and produce state

CMOS Growth drivers: Cloud infrastructure & Multi-screen clients

#### of the art CMOS in Europe that are able to address both the high performance end of the spectrum (3GHz+) and ultra-low power operation in order to serve the emerging multimedia applications and the new mini-servers and HPC markets

Basically application needs are exploding in three main directions generating a huge demand on silicon technologies.

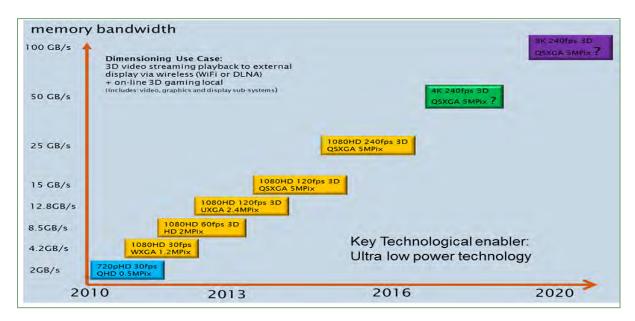

#### -Multimedia systems

There is an important trend for a continuous increase in terms of resolution and frame rate for multimedia sub-systems. This is a generic trend that is not only visible in the mobile industry. As a consequence, it is exerting strong pressure on memory bandwidth and the processing power needed to process these new data streams especially in the video domain. The graphic below shows the important evolution that has happened in the past few years and what can be foreseen in the future. Even if new codecs like the H265- HEVC are emerging to limit the file size explosion and maintain a good image quality, this occurs at the price of increased processing complexity which always requires more transistors to implement new functions.

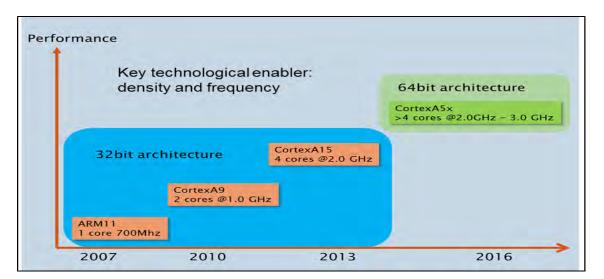

#### -Processing power

As shown in the figure below, a big change happened in the past ten years on the processor side and even bigger ones are ahead of us. In a few years, we moved from a relatively simple processing node to very complex systems which require very sophisticated memory hierarchy. This has a big impact on the technological complexity in order to sustain the good performance level of the overall computing system while maintaining a very strict control on the energy budget.

Once again the move from sub-GHz 32bit systems to multi-GHz 64bits systems will generate a tremendous increase in the number of transistors required. This is strongly pushing the technology to provide solutions able to fulfill the needs, but at the same time it is necessary to control the energy consumption to make sure it is still possible to manufacture the new system at reasonable costs.

A proper combination of memory technologies is needed to satisfy the requirements for access speed, memory capacity and power dissipation. New memory technologies like STT MRAM, or resistive switch memories are required to avoid that memory becomes a bottleneck for computing system. A proper allocation of memory types by cache level is required, with an optimized partitioning between memory integrated on-chip, in package or in dedicated high performance storage units (e.g. Solid State Disks).

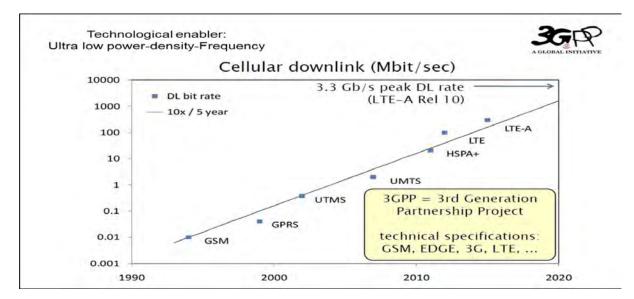

#### -Communications

In the communication domain, the evolution of the past year and the new trends are also generating a huge demand in processing and power efficiency. This has had a very important impact in a lot of domains because it allows new usage models with connected systems, increased volume of data exchange and this puts substantial pressure on both the client and the server side. This domain also has the requirement for more functions per silicon mm<sup>2</sup> in a more and more constrained energy budget.

#### 2.1.2 Current position

In production, MOSFETs have achieved the density, of typically, 35 transistors/ $\mu$ 2; making it possible for certain high performance circuits to exceed 1 billion transistors/chip. The minimum feature size printed onto the silicon for those chip is 28

nanometers. At this gate length dimension the conventional planar MOSFET becomes increasingly leaky and new transistor architecture is required. Next generations of technologies (below 28nm) will extensively use FULLY DEPLETED devices which can be implemented in various ways. These kinds of

devices require a very thin film of silicon to operate. We are entering the domain of thin film technologies at the same time as operating voltages reach below 1V and optical lithography becomes impractical economically due to the requirement of multiple exposures with complementary masks to print all the features drawn at a given level. Technologies become more complex, and expensive and therefore cost per function cannot decrease as much as it has in the past (cost reach the micro cent/transistor). Going forward, there are two options that are possible. We can either continue to drive for transistors with smaller footprint (and feature size) ie:

**more transistors per \mu2 OR** keep maintain feature size constant and stack thin film transistors on top of each other to generate **more transistors per \mu3**. Industrially a third option is possible to further decrease the transistor unit cost. In this scenario productivity improvements will be achieved with a leap in economy of scale by processing more chips at the same time, on each wafer (i.e changing the wafer diameter from today's state of the art 300mm to the future proposed standard of 450mm). This will have additional benefits and will require new manufacturing paradigms and equipment. This is an area where Europe is strong but research at this level is very expensive and resources will need to be husbanded very carefully in order to ensure that scaling up the technology platform doesn't diminish the ability to undertake research into device architectures and power reduction scenarios.

**Memories** are already now using feature size of around 20nm half-pitch, via double patterning, for NAND Flash, and 30 nm for DRAM. In the former, storage density is further increased by the use of multiple bit/cell. **Stored charge is however reaching it physical limits**, and no cost effective lithographic techniques is available to go below 20nm. **Going forward will require developing new memory technologies that are independent from charge storage**, like magnetic or resistive memories, and reducing cell footprint, and dependence on lithography by introducing vertical architectures. Low voltage memory technology is also required to integrate large quantity of non-volatile memory in advanced CMOS architectures, as required for microcontrollers used in most industrial and mobile applications.

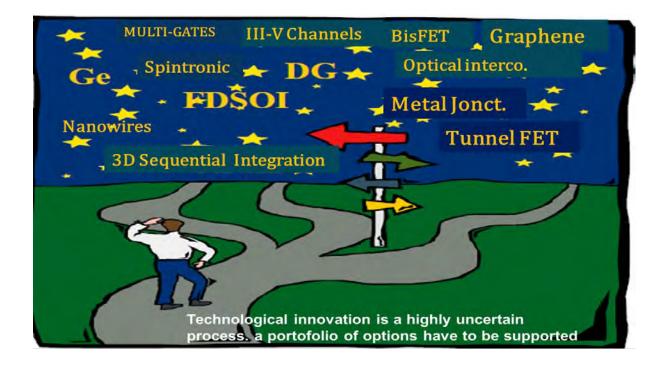

The international investigations for Ultimate CMOS and beyond-CMOS are covering the followings domains:

- **Implementation of advanced multi-gate structures for ultimate CMOS**. The challenges deal with the fabrication of advanced planar and non-planar multi-gate (common or independent gates) MOSFETs to 10 nm gate length and below, the control of short-channel effects, the control of threshold voltage and leakage currents, source/drain engineering to reduce parasitic resistance for thin film fully depleted (FD SOI) or fully inverted (FinFET, GAA...) devices, strain enhanced velocity and ballistic transport and alternative Ge/III-V channel materials and the use of substrate and channel orientation, and the improvement of the reliability of novel devices, structures, and materials with the control their failure mechanisms.

The reduction of sub threshold current and sub threshold slope, and the associate Vdd and power scaling, is of tremendous importance.

-In the charge-based/FET Beyond-CMOS field, which could extend CMOS scaling and/or performance (ultra-low power, new functionalities,...), the following Nanoscale FETs will be investigated: Nanowire FET, Tunnel FET, CNT FET, Graphene Nanoribbon or other 2D layers (MoS2, Silicene...) FETs. Other candidates are Negative gate capacitance FET, SpinFET, IMOS, Atomic switch, and Mott FET. For memories: vertical stacking of Flash cells, zero capacitor DRAM.

-In the non-charge-based, non-FET Beyond-CMOS devices, the possible candidates are NEMS switch, Spin wave devices, Nano magnetic Logic, Excitonic Field Effect Transistor, BiSFET, Spin Torque Majority Logic Gate, and All Spin Logic. For memories: magnetic memories, based on the Spin Transfer Torque effect (possibly thermally assisted), resistive switching memories like PCRAM and RRAM.

**Concerning ultimate processing**, the main investigations will deal with the continued scaling of SOI/multigate device (EOT, junctions, Si film, mobility enhancement, new channel materials, parasitic series resistance, contact silicidation...),. It will also see the introduction of high mobility channels (based on III-V and Ge) to replace strained Si, the EOT scaling below 0.7 nm with appropriate metal gates as well as the achievement of clean surfaces which are free of killer defects, and the introduction of 450mm wafers. With regard to lithography, EUV remains the leading candidate for 1X node and below, multiple patterning with EUV or reducing the EUV wavelength to 6 nm could also become options for the future. Alternative technologies are mask less E-beam lithography, Imprint, or direct self-assembly using the bottom-up approach for the very

long term options . With respect to novel interconnect architectures, researches are to be devoted to ultra-low- $\kappa$  materials with  $\kappa$ <2.0 and to introduce air-gaps, with a hybrid of low- $\kappa$

ultra-low- $\kappa$  materials with  $\kappa$ <2.0 and to introduce air-gaps, with a hybrid of low- $\kappa$  materials and air-gaps possibly being the best solution. TSV and 3D stacking technologies will also become of key importance.

In order to replace Cu, other metals (Ag, silicides ...), Nanowires, CNT, Graphene Nanoribbons, Topological insulators, Superconductors, and novel non-charge-based interconnects (Optical -interchip/intrachip, or Wireless), will need to be investigated.

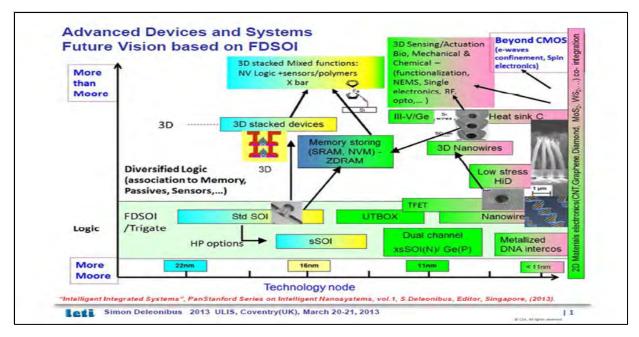

#### 2.1.3 Future vision

Issued from collaborative research at European level, a promising way to implement FULLY DEPLETED devices is through the **use of a thin film of silicon on top of insulator layer**: this technology using SOI substrate is called **FDSOI**. FDSOI can produce planar quasi double gate devices while a further option can be to use a thin vertical film of silicon (called fin) surrounded by the gate stack on 3 sides. This latter architecture is called a FINFET by some and a TRIGATE by others. The FINFET/TRIGATE architecture can also be built (with added advantages) on a SOI substrate or on Bulk.

At 14nm and possibly at 10nm the 2 architectures (planar (2D) FDSOI and 3D FINFET) will compete and will probably address different parts of the power spectrum (HP vs LP technologies). However, this trend towards thin film transistors could become a way to stack active transistor layers using the wafer bonding technique. It is envisioned to be able to stack multiple thin semiconductor films addressing the performance need of N and P type transistors (films could be of compound semiconductor materials or even single layer 2D crystals like graphene or MoS2). The

sequential stacking of transistors inside the same chip constitutes a monolithic 3D integration and it can be coupled to a 3D stacking of heterogeneous chips together by the 3D TSV technique. Ultimately, we foresee the possible combination of a 3D transistor architecture within a given semiconductor layer, a sequential layering of active films creating a 3D monolithic chip, and the 3D stacking of chips onto each other using TSV to interconnect them. The whole thing will create a highly compact electronic system.

For memories, the development of low power cross-point RRAM cell, will allow the stacking of several memory layers on the same CMOS substrate, thus allowing very high density memory architectures.

In the future, we will need to be less concerned about more transistors per mm2 and we will need to consider using more transistors per mm3 or more functions per mm3 as a metric. We need to think 3D More MOORE and 3D More Than MOORE (using as much as possible existing infrastructure). Stackable Transistor architectures would be preferred.

There are two ways to make a mixed technology three dimensional system:

- **By STACKING active semiconductor layers** within the same chip by some form of deposition or epitaxial approach where channel material would be the variable that would improve the performance

# -By STACKING heterogeneous chips onto each other and connecting by 3D vias called TSV (Through Silicon Vias).

Those two techniques are additive and a full system is envisioned (like an autonomous "zero power" system for the Internet of Things).

# For long term Beyond-CMOS options, which could be integrated on CMOS platforms, the most promising solutions are the following:

Multi-gates sSi, Ge or III-V Nanowires ; Heterogeneous Ultra-thin-body Multi-gates Tunnel FET, Fe Gate FET, NEMS and Spintronics for Ultra-low-power ; Graphene or other 2D layer (MoS2, Silicene,...), CNT channel MOSFETs and Tunnel FETs ; Controlled assembly of nanodevices or combined top-down and bottom-up approaches for Nanowires and CNTs.

#### 2.1.4 Areas of Cooperation

To remain at the forefront of state of the art for miniaturization and integration of nanoelectronic devices while dramatically increasing their functionalities, a coordinated European research effort is required in the following fields (including supporting fields):

- **Basic understanding** of the physical, chemical and electrical and magnetic properties **of materials and devices built at the nanoscale**. Modelling of the properties and devices from ab-initio models for deposition of material layers to compact electrical model in devices.

- **Multi-physics and multi-scale modelling methodologies** (e.g. first principle simulation for band structure, quantum transport, multi-sub band Monte Carlo, compact models including quantum and atomic scale effects, thermo-optical-electro-mechanical effects) for Nanoscale FETs used in future MM and MtM applications.

- **In-depth study of novel materials** with adapted behaviour and processes for high performance nanoFETs and new functionalities (e.g. passive and active components for RF applications, Optoelectronics). Examples where a strong effort is needed are alternative and uniaxial/biaxial strained channels (including Ge and strained Ge, III-V on Si, various orientations), Schottky barriers with dopant segregation techniques for source/drain, novel gate stack materials which go beyond Hf-based dielectrics, materials to improve interconnections of transistors.

- **In-depth study of novel materials** with adapted behaviour and processes **for high performance memory technologies** not based on charge-storage (e.g. magnetic materials, resistive switching materials, interface and isolation layers). These materials can be used also for the development of artificial synapses for neuromorphic computing architectures.

- **Novel interconnect architectures**, e.g. Optical interconnects as well as intraand inter-chip wireless interconnections, which could overcome the limitations of the traditional metallic interconnects.

- New device architectures for ultra-low power, high performance and memory or embedded memory applications, e.g. (independent) Multi-gate/Multi-channel MOSFETs, Tunnel FETs using ultra-thin films/alternative channel materials/multi-gates/1D structures, Si/Ge junction less and 3D integration of Nanowire FETs, Universal Memories combining volatile and non-volatile functions and usable for embedded memory applications.

- To be comprehensive, **new device architecture studies must include all aspects of their insertion into the technology platform;** such as impact on the design of elementary functions, compatibility with the design flow, variability in the manufacturing environment, testability of products, as well as intrinsic reliability under stress conditions.

- **Nano devices for adding functionalities to CMOS**, e.g. Nanowires for Nano sensing (thanks to the huge increase of its surface-to-volume ratio constitutes an ideal elementary block for highly sensitive sensors), Photovoltaic or Thermoelectric eenergy harvesting, or RF applications.

- **Physical** (e.g. roughness, dimensions, strain, dopant imaging, composition and density) and electrical (e.g. multiple interfaces and channels, surface states, transport, contacts, single impurity, variability/reliability, new physical mechanisms in very small volumes) **nano-characterization of nanoscale FETs**. Without those nano-characterization techniques it becomes impossible to ensure control and repeatability over the processing.Integration of very high densities of nanodevices by combining the top-down and bottom-up approaches using CMOS compatible technology.

- **3D Sequential Integration**: 3D integration is currently under great investigation because it offers a solution to continue to increase transistor density while relaxing the constraint on the transistor's dimension and it eases the co integration of highly heterogeneous technologies in comparison with a planar scheme. 3D sequential integration offers the possibility of using the third-dimension potential: two stacked layers can be connected at the transistor scale. This contrasts with 3D parallel integration, which is limited to connecting blocks of a few thousand transistors.

- **Development of ultimate processing technologies** (e.g. EUV lithography, multi-ebeam lithography, Nanoimprint, Atomic layer Deposition, Plasma ion Implantation, etc...) As well as next generation wafer size 450mm for the advanced technology nodes.

# 2.1.5 Roadmaps

| :                                     | 2014 2                                                                                                                                                                                                                                                                                             | 2017 202                                                                                                                                                                                                                                                                                                                                                                                    | 2023                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ULTIMATE CMOS                         | - <b>CMOS:</b> 2 <sup>nd</sup> gener. high<br>k/metal; Si+stress; S-D<br>engineering;<br>FD-SOI: Variability<br>/Reliability Transport<br>mechanisms (VRTM)                                                                                                                                        | Next generation highK metal K>30<br>E0I<0,7/0,8nm. Strained Si or<br>alternative Channel on SiGe IIIV-<br>Advanced S-D architecture –VDD<br>scaling, VRTM short channel<br>leakage model and characterization<br>1 <sup>st</sup> principle simulation/quantum<br>MSB MC simulations- Modeling<br>interconnectsof chemical<br>thermomechanical and electrical<br>properties of new materials | MG structure- 10nm MOSFET and<br>below, control of SC effects, TV and<br>LC, source drain engineering to<br>reduce parasitic resistance for<br>FDSOI or FinFET, GAA, devices,<br>and alternative Ge/III-V channel of<br>novel devices, structures and the<br>use of substrate and channel<br>orientation-failure control<br>mechanisms                                                                                                                                                                      |

| BEYOND CMOS                           | Nano wires bAssesment                                                                                                                                                                                                                                                                              | Carbon-based (Graphene,CNT,<br>FETs nanoelectronics with: -<br>high on-off ratio co-integrated with<br>high k dielectric and low resistance<br>contacts-Control of CNT<br>properties,bandgap distribution and<br>metallic fraction                                                                                                                                                          | Multi-gates sSi, Ge or III-V<br>Nanowires ; Heterogeneous Ultra-<br>thin-body Multi-gates Tunnel FET,<br>Spintronics r ; Graphene or other 2D<br>layer (MoS2, Silicene,), CNT<br>channel MOSFETs and Tunnel<br>FETs ; Controlled assembly of<br>nanodevices or combined top-down<br>and bottom-up approaches for<br>Nanowires and CNTs.*                                                                                                                                                                    |

| NOVEL<br>INTERCONNECT<br>ARCHITECTURE | -New materials to meet<br>conductivity requirements<br>and reduce the dielectric<br>permittivity -Electrical,<br>thermal, and mechanical<br>reliability -Three-<br>dimensional control of<br>interconnect features with<br>it's associated metrology -<br>Modeling and<br>characterization         | -Low-ĸ dual damascene metal<br>structures / air gap-Optical and RF<br>interconnects, CNT/Graphene<br>interconnects/via<br>-Identify solutions which address 3D<br>structures and other packaging<br>issues<br>-Modeling/characterization for new<br>interconnects                                                                                                                           | Ultra low-κ materials with κ<2.0 and<br>to introduce air-gaps, the hybrid of<br>low-κ materials and air-gaps could<br>be the best solution. The TSV and<br>3D stacking technologies will also<br>become of key importance.In order<br>to replace Cu, other metals (Ag,<br>silicides,), Nanowires, CNT,<br>Graphene Nanoribbons,Topological<br>insulators, Superconductors, and<br>novel non-charge-based<br>interconnects (Optical -<br>interchip/intrachip, or Wireless                                    |

| ULTIMATE<br>PROCESSING                | -Double and multiple<br>patterning<br>-EUV lithography -Atomic<br>layer Deposition,<br>MBE/MOCVD, High<br>aspect ratio dry etching,<br>Plasma ion implantation,<br>Plasma enhancement<br>PLD, Epi growthFront-<br>end process model. and<br>phys. /electr.<br>characterization for nm<br>structure | EUV lithography/extendibility :<br>*Higher source power<br>*Possible double patterning<br>*Possibly new resist<br>-193 nm immersion multiple<br>patterning<br>-Multi ebeams Maskless lithography<br>/ Imprint lithography<br>-450 mm wafers                                                                                                                                                 | Continued scaling of SOI/multigate<br>device (EOT, junctions, Si film,<br>mobility enhancement, new channel<br>materials, parasitic series<br>resistance, contact silicidation),<br>High mobility channels (based on III-<br>V and Ge) to replace strained Si, the<br>EOT scaling below 0.7 nm with<br>appropriate metal gates, introduction<br>of 450mm wafers.<br>Multiple patterning with EUV<br>Maskless-E-beam-Imprint, or Direct<br>self assembly using the bottom-up<br>approach for very long term. |

| 3D SEQUENTIAL<br>INTEGRATION | Thermal budget<br>management.<br>Electrical<br>contacts/silicidation.<br>Cleaning and surface<br>preparation<br>Intra-layer interconnects                                                | Strained and/or orientation<br>optimised materials on each level.<br>N/P over P/N and/or CMOS/CMOS<br>solutions.<br>Co-integration with resistive<br>memories within interconnect and in<br>intra-layer Interconnects schemes.<br>Mix 3D and TSV for system<br>solutions | New high mobility materials.<br>Extension to three or more device<br>layers. Vertical structures.<br>Interconnection congestion<br>management.<br>Deep field of focus litho (e-beam)<br>Photon/electron sensitive materials<br>for litho |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MEMORY<br>ARCHITECTURES      | Charge storage: - vertical<br>cell architectures, - new<br>capacitor materials for<br>DRAM<br>Non-charge storage:<br>- STT memories, -<br>multilevel PCM memories,<br>- cross-point RRAM | Non charge storage:<br>Higher density MRAM<br>memories,Multi-layer, multi-bit<br>RRAM memories                                                                                                                                                                           | Non charge storage:<br>- 3D integration of different memory<br>architectures;<br>- molecular memories                                                                                                                                    |

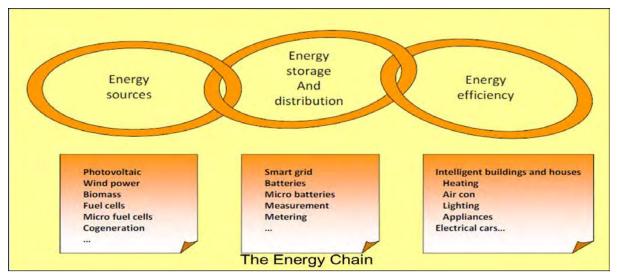

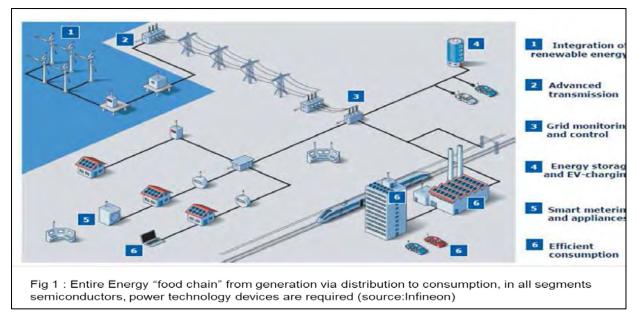

### 2.2 Smart Energy

The "Smart Energy" terminology has been defined for nanoelectronics solutions dedicated to all energy-related applications and markets. Covered under this umbrella are **technologies, materials, integration methodologies and processes for the realization of more energy efficient devices and systems.** Technologies combining the integration of power semiconductors with "smart" feature capabilities and new materials, in order to provide high efficient all-in-one "power", in System-on-Chip (SoC) or System-in-Package (SiP) forms are addressed. "Smart Energy" also covers the market introduction and penetration of **a new class of power devices based on wide band gap semiconductors such as SiC, GaN or AlN.** Strengthening the European research and innovation infrastructure in these areas will enable Europe to be a leading provider for all kind of solutions dealing with the intelligent use, generation and distribution of energy, in particular: Renewable Energy, Intelligent Buildings, Smart Grid, Electrical

#### Vehicles.

Being an "open innovation" circle, new topics brought in by the partners and evolved from the discussion amongst the partners will be covered. The objective will be to create a clear understanding regarding a sustainable roadmap for the different smart energy related technologies, the needs for a collaborative development set-up and a clear identification of the win – win opportunities of cross-border partner collaborations.

Changes are always fundamental for success and leadership. **The emerging European market in this sector is huge, and the room for new "Smart Energy" solutions and associated enabling semiconductor technologies is correspondingly large.** Strengthening the European research and innovation infrastructure in this area will enable Europe to be a leading provider of all kind of solutions dealing with the intelligent use, generation and distribution of energy.

The world in the  $21^{st}$  century has to cope with growing worldwide population, limited conventional energy resources, climate changes and the need to reduce  $CO_2$  emissions. All this is challenged by the wish of the individual persons to reach, keep or even improve their European lifestyle. Highly efficient and intelligent use of energy is a key enabler to solve these socio economic challenges. The yearly market growth rate for energy related semiconductors is expected to be above 10% and new applications are, from a global perspective at the beginning of their success story.

The "Smart Energy" battle is now very engaged at a worldwide level and represents a true challenge. Such a high level cooperation as is planned within ENI2 is necessary in order to achieve the whole R&D and production cycle to the benefit to the overall European society. The full know-how and process chain (starting from raw wafer materials up to the end-products) must be addressed.

#### 2.2.1 Applications needs

#### -Energy sources

DC/AC converters for solar power, AC/AC converters for Wind power: modules, switches, diodes, ICs supporting highest energy efficiency in power conversion

Panel switch: intelligent switch for individual control of photovoltaic solar panels, and communication ICs.

- Smart "Sun tracking": intelligent motor control for orientation of photovoltaic solar panels (+30%)

#### -Energy storage and distribution

- High voltage smart switches for grid coupling and energy transport in AC/DC/DC/AC for HVDC (High Voltage Direct Current)

- Smart grid monolithic AC switch with high galvanic isolation, very low  $R_{\text{on}}$ , self-powered, over current, voltage, temperature protected, full control and status indication, communication

- Smart meters with contractual electricity consumption measurement and communication features.

- Power switches for energy crossroads and routers for individual energy sources Management

DC- DC converters for direct DC use from wind or photovoltaic sources in the connected neighborhood (retail houses, manufacturing sides, office/large buildings)

Highly efficient converters for all kind of bi-directional energy flow for intermediate storage applications

#### -Energy efficiency

#### Intelligent Buildings

- Energy scavenging systems (temperature/light/vibrations) for self-powered sensors: a very generic architecture including energy sensor, thin film micro battery for storage, power management IC, building parameter sensor (temperature, pressure, humidity, light, windows and doors position, chemicals, air quality, human presence, human activity...), data recording and computing, and full communication features (RF)

- Lighting applications

- Smart plugs

- Smart energy breakers

#### -Electric cars (e-cars)

- Power switching modules in motor drive inverters

- Battery management and reverse protection

- Energy braking recovery system

- High power traction

#### -Substitutions of mechanical or hydraulic systems

- DC bus systems with intelligent controllers and switches

- Electric drivetrains in conventional applications

#### 2.2.2 Current position

In "low-medium voltage", and due to the good performance of silicon in this range, "**Up-to-150V Smart Power" is continuing to take profit from the silicon mainstream** in terms of fundamental operations, i.e. lithography, implantation and CMP. Silicon CMOS-based Smart power ICs will continue to address new challenges into the coming energy-related applications, and can take benefits from both "More Moore" (MM) and "More than Moore" (MtM) results to be achieved on silicon during the coming years. **Above 150V** and definitely beyond 600V, i.e. for alternative energy markets, intelligent buildings, smart grid, electrical cars and more... **silicon still offers room to improve its performances** and it will do so, especially looking at improving MOS-IGBT-JFET switches.

#### 2.2.3 Future vision

New "wide band gap semiconductor materials" are much more promising in offering higher performant switching cells composed of Schottky diodes plus MOS-IGBT-JFET switches. Gallium Nitride (GaN) and Silicon Carbide (SiC) offer better voltage ( $100V/\mu$ m instead of  $10V/\mu$ m in silicon) and much higher temperature operation ( $200^{\circ}$ C instead of  $125^{\circ}$ C). Although these materials are very interesting, they require the development and control of new processes like homo epitaxy, hetero epitaxy on silicon, localized epitaxy, and also the design of very new device architectures. Diamond, as the Holy Grail to conquer, would offer  $1000V/\mu$ m and as well as definitively the best class in term of heat dissipation. These new semiconductor materials with higher junction temperatures will ultimately lead to new challenges and research for the integration into packages, for bonding and for the connection to heat dissipation systems.

Generic architecture of a "Smart energy" product

The "Smart" side which brings intelligence and numerous added features to the "Energy" side is typically using "very low voltage" (a few volts) and it may also require new materials in the "More Moore" and "More than Moore" challenges (CMOS, Ultimate CMOS, beyond CMOS, Heterogeneous/3D integration and packaging). In addition, **all these derivatives have to be compatible with a "Power" environment** and consequently they may have to be made for their operating conditions e.g. it might be necessary to investigate( DSP core, CPU or memory immunity during an high current switching operation with the additional complexity of adding operation at high junction temperatures).

**Integration of "Smart" and "Power**" will be achieved either under single-chip form (when materials and processes are compatible) or 2D/3D multi-chip combination, always looking at optimizing global performance-to-cost ratio.

#### 2.2.4 Areas of Cooperation

Overall picture: ENI2 is an initiative from core partners within the European semiconductor community. A solid top level base has been set by the AENEAS AWP for future research activities. For the "smart energy, domain the relevant topic in the AWP is the chapter on Energy Efficiency including the specific Grand Challenges and the dedicated topics within the chapters Design Technology, Semiconductor Process and Integration and Equipment, Materials and Manufacturing.

#### • Materials and associated processes

- In addition to silicon ( $10V/\mu m$ ), new materials dedicated to "Power" are necessary, along with a road map going through Silicon Carbide and Gallium Nitride ( $100V/\mu m$ ), and then ultimately to Diamond ( $1000V/\mu m$ ). New materials and structures for voltage isolation are also a key issue. The associated manufacturing processes must be widely developed, with a specific focus on epitaxy (homo epitaxy, hetero epitaxy on silicon, localized epitaxy) because traditional implantation and doping processes are inefficient and difficult to achieve for these new materials. Processes must be compatible with mass production, cost objectives and further integration into appropriate packaging. The reliability aspects have to be considered on top, since the typical automotive domain applications are in long term usage as in infrastructure elements or for the use within the automotive domain.

- New materials dedicated to the "Smart" side are necessary in order to bring derivatives outside the CMOS mainstream. For instance, sensors, micro supply, micro energy sources and micro batteries, transformers, transducers, and integrated passives represent high added value to energy-related "Smart energy" products. These devices must be compatible with further integration.

- However, in addition to semiconductors, two main challenges have to be solved to leverage the full benefit of advanced innovative semiconductors for "smart energy" and it is important to acknowledge these and anticipate the upcoming requirements. These are;

- New materials, dedicated to improve large value capacitors and inductors used in power conversion architectures, and high temperature capable package and integration technologies have to be developed to cope with the capabilities of the new materials for semiconductors.

#### • Architectures

Whatever the materials, new architectures are also necessary to allow higher "Power" performance, and among them, 3D is a key issue. This is true on the electrical, thermal, magnetic, and mechanical aspects.

"Smarter" and "Smarter" chips are being requested, to handle future complex systems solutions allowing full control, complex data storing and computing, with automatic sensing and instantaneous status feedback etc.. ....

#### • Simulation Tools

State-of-the-art simulation tools are today dedicated either to electrical, mechanical, thermal, optical or magnetic strength fields. Some tools have started to offer a mixture of the different domains but, for "Smart Energy", very significant improvements still remain necessary to achieve in order to simulate the true physical material and behavior of architectures, required to reduce development cycle times and costs.

#### 2.2.5 Roadmaps

|    | 2(                                       | 014 20                                                                                                                                                                                                                                                                 | 17 20                                                                                                                                                                                                                                   | 2023                                                                                                                                                                                                                                                                                                                                              |

|----|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. | COMPOUND<br>MATERIALS /<br>New Materials | -SiC<br>-III-V materials knowledge<br>from CMOS to power<br>-Materials for capacitors,<br>inductors<br>-Growth of GaN in comb.<br>with high k.<br>-MIM devices for RF<br>-Carbon Based Graphene<br>Nanoelectronics<br>Technologies : ft .5THz                          | -GaN<br>-On SOI med. Power<br>-New materials and<br>associated processes for<br>Smart derivatives<br>compatible with power<br>-High power GaN devices<br>suitable for PV applications<br>-GaN/Si tandem PV cells<br>-MIM devices for RF | -Sapphire, Diamond<br>-New materials and associated<br>processes for Smart<br>derivatives compatible with<br>power<br>-Piezo NEMs for energy<br>harvesting; Thermoelectric<br>nanodevices;<br>-RF and THz energy<br>scavenging based on TFT and<br>MIM antennas<br>-Carbon Based Graphene<br>Nanoelectronics Technologies:<br>ft higher than 1THz |

| 2. | INTEGRATION<br>OF SMART<br>AND POWER     | -Sensors, logic, etc. with<br>power Integration<br>-technologies for energy<br>harvesters                                                                                                                                                                              | -Sensors, logic, etc. with<br>power<br>-Energy harvesters                                                                                                                                                                               | -Energy harvesters                                                                                                                                                                                                                                                                                                                                |

| 3. | PACKAGING                                | -Hot spot resistant<br>packages                                                                                                                                                                                                                                        | -New 3D power semic.<br>Architecture<br>-Hot spot resistant<br>packages                                                                                                                                                                 | -Hot spot resistant packages, connections,                                                                                                                                                                                                                                                                                                        |

| 4. | PROCESSING                               | -SiC >1kV<br>-GaN on Si<br>-Low power mixed signal<br>& RF<br>-Logic with HV<br>applications<br>-300mm power producton<br>technology<br>-Material deposition – e.g.<br>Laser, spray, sputter, ALD<br>and characterisation of<br>ultra-thin dielectric multi-<br>layers | -SiC >1kV<br>-GaN on Si<br>-Low power mixed signal &<br>RF<br>-Logic with HV applications<br>-300mm power production<br>technology<br>-Material deposition<br>processes and<br>characterization of ultra thin<br>layers                 | -Diamond<br>-Saphire<br>-Material deposition processes<br>and characterization of ultra<br>thin layers                                                                                                                                                                                                                                            |

# 2.3 Smart Sensors

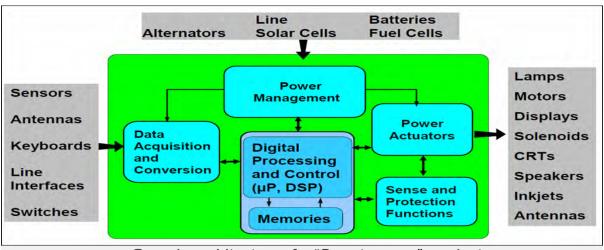

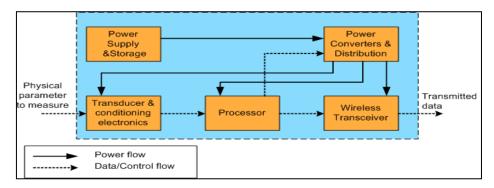

A smart sensor is made of a measurement chain composed of a sensor (also called transducer that transforms the sensed parameter into an electrical signal), some analogue conditioning electronics, a processor and a wireless transceiver as well as a power distribution chain composed of a battery or energy scavenger and of a power management unit.

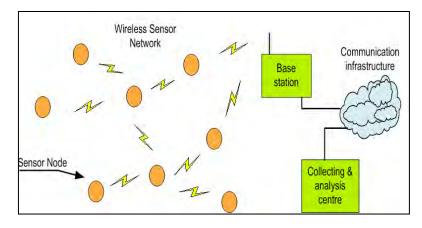

But a smart sensor is not an isolated element. It is an element of a system that constitute an application. The system may be quite simple for the measurement of the heart rate of a runner or quite complex as illustrated in next figure (e.g. for the global monitoring of the physical condition of a team during a football match)

#### 2.3.1 Applications needs

The expected economical and societal impacts of smart sensors<sup>1</sup> applications are huge. The yearly market growth rate for smart sensor related semiconductors is expected to lie between 10% and 40% depending of the application domain. Miniaturized healthcare monitoring sensors will contribute to maintain patients out of the hospital and reducing the impact of healthcare on the national budget. Autonomous sensors will avoid heavy cabling in cars and thus reduce their weight and fuel consumption. Applied to buildings, smart sensors are enablers for intelligent lighting and temperature control. Other applications are the monitoring of the structural health of bridges or windmill motors, the control of the irrigation or watering of soils in agriculture, the lighting-onneed of parking and public places for minimizing the power consumption and for improving the security, etc...

A smart sensor will rely on various heterogeneous technologies like analogue, digital and RF (Radio Frequency) electronics, such as MEMS (Micro Electro Mechanical System)

<sup>&</sup>lt;sup>1</sup> A smart sensor is made of a measurement chain composed of a sensor (also called transducer that transforms the sensed parameter into an electrical signal), some analogue conditioning electronics, a processor and a wireless transceiver as well as a power distribution chain composed of a battery or energy scavenger and of a power management unit.

or photonics for energy scavenging and chemical for the battery/power supply. It may also rely on fluidics, pneumatics, optics, chemical, biochemical or mechanics for the transport of the samples to analyze and for their characterization. The link of the smart sensors with the domains of heterogeneous integration and smart energy is obvious but some other more specific research domains should also be considered. These are: energy scavengers, transducer and actuator technologies, low-power communication protocols for low duty-cycle smart sensors, low-leakage components, low-power sensor node architecture, modeling and simulation technologies...

#### 2.3.2 Current position

"Smart sensors" is a rather new application domain. Current applications are limited to some specific cases: with high added value markets like the industrial market (automation...) and health market (hearing aids). Current products are rather expensive, generally power hungry, and exhibit large size...

The number of potential applications is rather large but entering these markets could mean cheaper, smaller size, lower power, integration of new technologies...

In order to enable the realization of these new products, effort is needed in various technological domains and this effort cannot be supported by a single partner... Therefore cooperation will be instrumental in making progress in this domain for European industry

#### 2.3.3 Future vision

This multiple integration of a variety of technological options and the request of autonomous energy efficient smart systems requires strong academic industrial collaboration research. In particular, the long-term R&D efforts might include 3D smart multi-functional materials and novel circuit architectures, sensors & integrating multifunctionalities biotechnology, actuators (mechanical, nanotechnology, photonics....) and ultra-low power solutions. Modeling, simulation and characterization of such a kind of integrated multi sensor have to be performed and experimental progresses have to be evaluated in an industrial environment. MEMS based smart sensors technology opens the door to a new generation of micro-nano scale, innovative sensors to serve key market applications in Automotive, Industrial, Consumer, Telecommunication and Medical markets.

#### 2.3.4 Areas of Cooperation

The need for integration of various technologies and the request for autonomous energy efficient smart systems require strong academic industrial collaboration research. In particular, the long-term R&D efforts might include:

• Nanoscale structures:

-Nanowire, carbon nanotubes, graphene for improving intrinsic device performance or for enabling new functionalities

- Ultra low power solutions: - For electronics, for software and for wireless communications

- Integration on/within textile

- Implantable sensors: -Biocompatibility and interfacing electronics

-Modeling, simulation and characterization of integrated multi sensors for experimentation of for evaluation in an industrial environment.

• Heterogeneous smart sensors:

-MEMS, biotechnology, fluidics...) for applications in automotive, industrial, consumer, telecommunication and medical market

- High efficiency, low-leakage (thin, flexible, printed) batteries

- Standardization:

-Communication, hardware and software interface between key building-blocks

• Micro storage devices, architecture and materials

#### 2.3.5 Towards Roadmaps-Proposed methodology

The application space of "smart sensors" is very broad and each application has its own specific requirements. Although the global architecture is similar for all applications, there is no single design that can satisfy all applications. A "smart sensor" application could rely on various technologies, but all of them are not necessarily needed for each application. What is more when a set of applications requires the same technology, all of them do not necessarily require the same maturity level or the same performance level for the needed technology.

As a consequence, the roadmap for a given application (or set of applications) cannot be dissociated from the roadmap of its enabling technologies. The application roadmap of some promising applications should be consequently linked with the roadmaps of the "smart sensor" enabling technologies. Taking into account the number of scenario related to the applications requirements and their associated targets, we have agreed to limit our work to the definition of the methodology to be used. Detailed road mapping activities have to be pursued in the context of ECSEL, CATRENE and HORIZON 2020.

Proposed methodology: we have to combine following three different point-of-views and to combine them into a single view for each considered application.

#### • Applications point-of-view

Looking at the most promising applications (market potential, added-value for the consumer, sustainability, for taking a world leading position...) Looking long-term with intermediate steps...

→ Result: list of promising applications

• "Architecture and building blocks" point-of-view

Looking at the smart sensor architecture and its critical building blocks → enabling new applications (although the ones we are not able to think about, today )

$\rightarrow$  Result: list of new enabling building blocks

"Enabling technologies" point-of-view

Looking at the technologies (not necessarily specific, incl. tools, standards) that will enable the realization of smart sensor applications

→ Result: list of enabling technologies

#### **Point of-view Applications**

The Preliminary list of sensor networks application is based on the ontology from Libellium (http://www.libelium.com/top\_50\_iot\_sensor\_applications\_ranking/) and Beecham Research (<u>http://beechamresearch.com/article.aspx?id=4</u>)

- Medicine & Health

- Automotive & Transport

- Plant construction & engineering

- Materials testing

- Process and environmental monitoring

The domains of applications and the related products are very broad with large diversity in their requirements; moreover the technological improvement (roadmaps) will not impact the progress in all application domains in the same way.

Some of the product requirements are depending on the progress made in the technological domains (building-blocks and technologies). The technological progress in the various technological domains will be evaluated in term of the main sensor application drivers, which are:

-Physical properties (size, form factor, readiness/flexibility/stretchability for integration in textile...)

-Power consumption (mean, peak, towards autonomy by harvesting)

-Cost (initial cost, incremental cost...)

-Functionalities (sensed parameters, precision...)

-Infrastructure deployment readiness (servers, communication, IoT, supportive tools & modeling...).

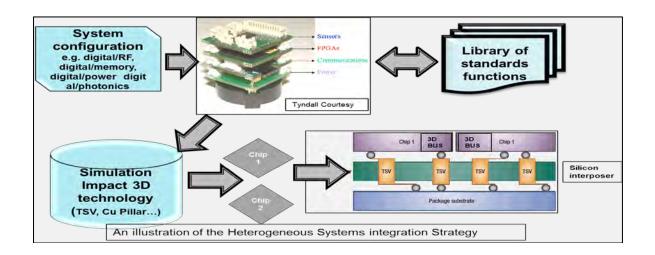

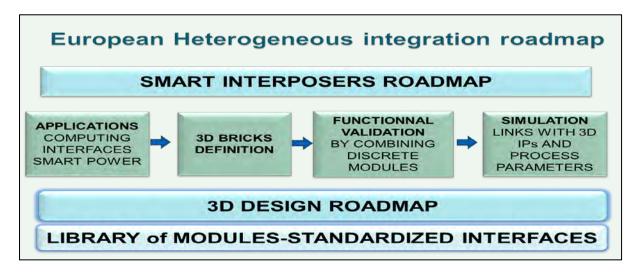

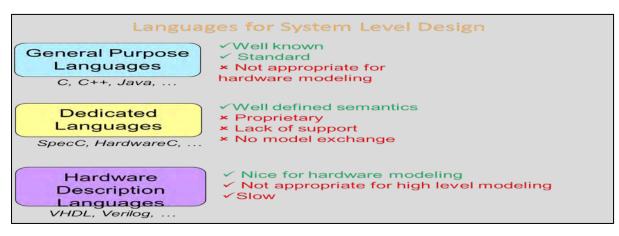

#### **Point-of-view Architecture**