## CATRENE

## Project Profiles and Result Sheets

## CATRENE Project index

CA101 | PANAMA

CA103 | HERTZ

CA301 | HIDROLON

CA303 | OPTIMISE

CA501 | COMCAS

CT105 | 3DIM3

CT204 | PASTEUR

CT301 | EXEPT

CT302 | TOETS

## Call 2

CA104 | COBRA

CA202 | eGo

CA402 | THOR

CA502 | SEEL

CT205 | REFINED

CT206 | UTTERMOST

CT207 | COCOA

## Call 3

CA308 | ICAF

CA403 | RELY

CT208 | REACHING22

CT209 | RF2THZ SiSoC

CT305 | SOI 450

CT306 | NGC450

CT402 | 9D-Sense

## Call 4

CA109 | SHARP

CA110 | AppsGate

CA111 | UltraHD-4U

CA206 | NewP@ss

CA310 | EM4EM

CA701 | H-INCEPTION

CT210 | DYNAMIC-ULP

CT213 | 3DFF

CT312 | MASTER 3D

## Call 5

CA112 | HARP CA505 | BENEFIC CA703 | OpenES CT315 | EmPower

## Call 6

CA114 | WiCon

CA116 | CORTIF

CA118 | FITNESS

CT217 | RESIST

CA208 | MobiTrust

## Call 7

CAT120 | CISTERN

CAT121 | EAST

CAT406 | NEMADE

CAT801 | TSV-Handy

CAT802 | SAM3

CAT209 | H2O

CAT601 | SiPoB-3D

## Call 8

CAT311 | TRACE CAT408 | NexGen

E450LMDAP is a co-labellled project with ENIAC JU. For more information on this project, please see www.eniac.eu.

# CALL 1

# issues helps ensure future success of mobile

## communications [PANAMA]

As the use of mobile phones, especially the smart variants, grows from strength to strength with increased subscribers chasing even more functionality, capacity and performance, behind-thescenes issues relating to networks and handsets need to be addressed if this momentum is to be sustained. That's where PANAMA comes into its own. This project has successfully exploited the expertise and experience of leading European partners from the semiconductor, test tools, electronic design automation industries, and academic institutions in dealing with critical issues. This collaboration between industry and academia also demonstrated the value universities, with their wealth of knowledge and research resources, can bring to a partnership, something entrepreneurs on both sides are taking advantage of.

PANAMA brought together a large consortium of project partners with specialist expertise, from various industries, such as semiconductor, test tools and electronic design automation, but also from academia. They focused on a wide range of advanced application areas and systems (integrated, discrete and distributed), such as multi-band, multi-mode and more efficient power amplifiers and transmitter systems for mobile handsets, as well as, base transceiver stations, avionics, mobile satellite communication and home networking.

Project activities included:

- Designing and developing key components,

- Improving system efficiency,

- Developing standards and design methodology,

- Developing models and simulation and characterisation tools,

- Promoting PANAMA and disseminating project results/achievements through the internet, scientific publications, and workshops and conferences.

## Surpassed initial goals

Clear project goals were assigned at the start:

- 20% efficiency improvement for integrated systems

- 30% efficiency improvement for discrete sys-

tems

10% efficiency improvement for distributed systems

All tasks were completed on time, deliverables achieved and initial goals met. What is more, techniques (developed or optimised) relating to integrated and discrete systems – 26/3G mobile applications, home networking, base stations, airborne and satellite communications – even surpassed initial targets.

## Good project-participation mix

A fine example of pan-European collaboration, PANAMA was a strongly industry-focused project that attracted more than 20 participants from five countries, and where universities played an important role in resolving 'roadblocks'.

In line with other CATRENE projects, PANAMA's activities, tasks and deliverables were divided into 'work packages' (WPs), to which project partners were assigned based on their skills and expertise. Notably, WP4 provided the tools essential to the activities in other WPs.

Internal collaboration was excellent, ensuring a smooth and successful operation. A sign of good co-operation and engagement among partners was reflected in the high attendance at project review

### Partners:

Agilent Technologies Belgium

Amcad Engineering

CEA-LETI

**ELTA Systems**

ESIEE Paris

Gigle Semiconductor

**IEMN**

ıms

Institut Telecom

KU Leuven

$MC^2$

NXP Semiconductors FRA, NLD

OMP

ST-Ericsson Belgium

STMicroelectronics

THALES Communications

TNO

TU Delft

TU Eindhoven

**UPC-HiPICS**

## Project leader:

Philippe Meunier

NXP Semiconductors

## Key project dates:

Start: January 2009

End: September 2012

## Countries involved:

Belgium

France

Israel

The Netherlands

Spair

## PROJECT CONTRIBUTES TO

| Communication            |    |

|--------------------------|----|

| Automotive and transport |    |

| Health and aging society | \\ |

| Safety and security      | \\ |

| Energy efficiency        |    |

| Digital lifestyle        |    |

| Design technology        |    |

| Sensors and actuators    |    |

| Process development      |    |

| Manufacturing science    |    |

| More than Moore          |    |

| More Moore               |    |

|                          |    |

meetings. This was also reflected in the number of joint publications (many involving partners from industry and academia) and patents, as well as, workshops organised by and for project members

## Putting PANAMA's deliverables to good use

Most importantly, PANAMA will offer mobile users handsets with batteries that are even more energy-efficient, as well as, faster, higher-capacity internet connections, with even more access-points. This also means that service providers will have satisfied clients with an even greater appetite for mobile and web services.

Behind the scenes, PANAMA delivered, first and foremost, tools needed to support its own project activities. The nonlinear characterization tools led to faster and more automated and accurate measurement-taking and harmonic matching, as well as, support for low- and high-power for devices under test, new measurement possibilities and with higher frequency. Importantly, these tools did not require the normal high-level of expertise to operate them.

Nonlinear models developed were more accurate. Thanks to improved extracted models, a Power-added Efficiency increase of 10%-15% was achieved and model extraction simplified. Simulation tools increased functionality and performance, surmounting current limitations.

Then there were deliverables whose benefits went beyond the project boundaries. A new architecture and design methodology developed in PANAMA will lead to future improvements in transmission efficiency. From an academic point of view, universities and research laboratories increased their expertise through the 15 PhD students trained in PANAMA, the three patents issued, and the 137 papers published in prestigious journals or presented at international conferences. And stand-

ards established during joint-development work developed by NXP and TU Eindhoven on Beamformer and down-tilt antenna for base stations have been submitted for acceptance to the international Antenna Interface Standards Group, AISG. of which NXP is member

Some deliverables and contacts even had commercial consequences outside the actual project. Firstly, a start-up, Anteverta-mW BV, was created by TU Delft to commercialize the active harmonic load-pull test setup developed in the project. And the first customer was a PANAMA partner, NXP.

Next, the transfer of expertise from academic partner to industry is also going well. More generally, there are several cases where architectures and circuit components developed through the collaboration between university and industry are being deployed by the industry partner.

Finally, to quantify the accuracy of the measurements using the nonlinear characterizations tool benches, IEMN developed a nonlinear reference component called the 'Golden Device'. It is capable of quantifying the accuracy of nonlinear measurements, and is currently being used by other European laboratories.

Looking to the future, PANAMA's innovative deliverables and other project output are also available to European integrated circuit (IC) manufacturers and system providers, for example, and can be deployed as part of their defence against external competition.

## **CATRENE Office**

9 Avenue René Coty - F-75014 Paris - France

T. +33 1 40 64 45 60

E. catrene@catrene.org www.catrene.org

**CATRENE** ( $\Sigma$ ! 4140), the EUREKA **C**luster for **A**pplication and **T**echnology **R**esearch in **E**urope on **N**ano**E**lectronics, will bring about technological leadership for a competitive European information and communications technology industry.

# CA103 | Energy-Efficient Home rtz Networks [HERTZ]

Energy efficiency is high on the European agenda. However, even with the arrival of regulations to phase out incandescent lamps and the introduction of various forms of energy-efficient lighting, a significant amount of energy continues to be wasted in homes and offices. The main contributor to this situation is that lights or other appliances are often left on when they are not required. The CATRENE HERTZ project has taken the first steps towards the introduction of auto-adaptive networking devices that limit energy wastage in both domestic and commercial equipment, without human intervention.

## Auto-adaptive consumer networks lead the way in energy saving

For many years, it was thought that the home automation market was on the verge of centralised control or networking of all electrical appliances, from the washing machine to the refrigerator to the television to lighting. It has long been acknowledged that true energy efficiency requires automatic control systems.

However, in order to help the expansion of the market for such consumer networks, the members of the HERTZ consortium identified key challenges that had to be confronted. Firstly, it was essential to analyse the power consumption of such a network and to demonstrate that the amount of energy saved was greater than the amount of energy needed to make the saving. The consortium then worked towards a solution that is easy to use and can be installed by an ordinary consumer without having to rely on a professional. Finally, they addressed the issue of compatibility between proprietary devices and the risk that their presence in isolated clusters would hinder market development. All of these challenges were examined by the consortium while, at the same time, aiming to minimise the cost for the consumer.

The results of the Hertz project have led to substantial progress in this domain (sometimes called the Internet of Things), with the establishment of a set of standards that will form the basis of a compatible home automation network of the future.

## A comprehensive solution

Over the three-year duration of the project, the consortium members worked together to establish a scenario that will serve as the European basis for the future energy-efficient networking of home appliances. The goal was to provide the means of controlling the functionality of disparate devices in such a way that overall efficiency is substantially improved.

The first stage in this process was to address the use of lighting energy. A large step was already taken with the phasing out of low-efficiency incandescent light bulbs. The next step has to be the efficient use of the new low-energy light sources and especially solid-state lighting (SSL). In fact, the efficiency of SSL lighting is already so good that it's a challenge to see how existing wireless networks could be used to control lighting without wasting energy. This is very much the case with

### Partners:

ADD Semiconductor (acquired by Atmel)

Dialog Semiconductor

DS2 (acquired by Marvell)

Infineon Research

Infineon Wireline Division (spun out as Lantiq)

Iquadrat

Iquadrat

Philips Consumer Electronics (spunout as TPVision)

Philips Lighting

Philips Research

Quintor

## Project leader:

Henk Schepers Royal Philips Electronics

## Key project dates:

Start: October 2009 End: September 2012

## Countries involved:

Austria Spain

The Netherlands

## PROJECT CONTRIBUTES TO

| Communication            |          |

|--------------------------|----------|

| Automotive and transport | / /      |

| Health and aging society |          |

| Safety and security      |          |

| Energy efficiency        |          |

| Digital lifestyle        |          |

| Design technology        |          |

| Sensors and actuators    |          |

| Process development      |          |

| Manufacturing science    |          |

| More than Moore          |          |

| More Moore               |          |

| Technology node          | 45/32 nm |

WiFi systems, which have been shown to waste 80% of the energy in protocol maintenance while only 20% is used for data transfer. Providing SSL users at home or in the office with more comfort and safety without wasting energy is not easy using existing WiFi protocols.

Consumer acceptance dictates 'no new wires'. Where possible the existing electrical infrastructure will be used to power a sensor or to exchange information between system components (powerline communication) but, preferably, wireless control and mains-free power is required. The challenge was, therefore, to first of all devise new wireless methods of connectivity that are substantially more energy-efficient. To enable battery-free operation and to avoid frequent battery replacements, a second challenge was to develop much more precise sensors. Furthermore, the accuracy of those sensors had to be improved to ensure consumer satisfaction.

## **Dedicated components**

The HERTZ project has successfully addressed component-level technology concerns, by creating an energy-efficient true presence sensor, a fully-harvesting powered daylight sensor and a wireless clip-on power sensor allowing disaggregated power measurements.

To achieve much more energy-efficient wireless networking, the HERTZ project has brought about the development of:

- a bi-state receiver concept with a wake-up sensitivity of -90 dBm at only 5 μWatt

- an ultra-low energy (ULE) variant for DECT with a sleep-mode consumption of 3 µA instead of the continuous 2.2 mA for normal DECT and a burst-mode consumption of only 2 mC

- an energy-efficient wireless local area network (WLAN) stack that performs up to 90% more efficiently in specific use cases

a power adjustment scheme for the ZigBee wireless specification that leads to a 27% reduction in consumption.

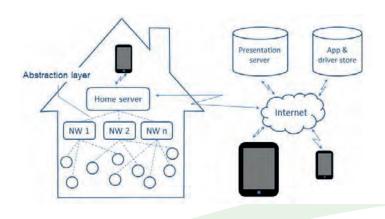

The HERTZ project has also defined a gateway interface specifically tailored to the integration of different network technologies. As the various HERTZ members are leaders in their respective fields, the expectation is that this interface will help to give a realistic boost to the development of the home energy-control market.

Finally, the introduction of a self-configuring application and driver store provides for simple plug-and-play system installation.

## The basic infrastructure

As a result of the HERTZ project, the control and/ or monitoring of energy consuming appliances, in the home or in a commercial environment, has become a reality. The true presence sensor provides the means of determining a human presence in a room, even if the subject is motionless. The HERTZ gateway offers a means of wirelessly interfacing to a wide range of other devices that can signal their status over the network. The network protocols developed in the HERTZ project set standards that appliance manufacturers can use to enable their products to communicate, eliminating the incompatibilities that restrict the average consumer.

Overall, the HERTZ project has created the basic infrastructure for a comprehensive network control system that will greatly improve the efficiency of energy consumption in homes and commercial premises. It is confidently expected that electrical appliance manufacturers will, in future, follow the trend of providing their products with external interfaces conforming to the standards developed in the HERTZ project.

## **CATRENE Office**

9 Avenue René Coty - F-75014 Paris - France T. +33 1 40 64 45 60 E. catrene@catrene.org www.catrene.org **CATRENE** ( $\Sigma$ ! 4140), the EUREKA **C**luster for **A**pplication and **T**echnology **R**esearch in **E**urope on **N**ano**E**lectronics, will bring about technological leadership for a competitive European information and communications technology industry.

# CA301 | High Dynamic Range Low Noise HIDR LON CMOS imagers [HiDRaLoN]

The purpose of the CATRENE HiDRaLoN project was to address societal needs in such areas as healthcare. entertainment as well as road and industrial safety. The results are expected to provide greater efficiency and fewer errors in medical diagnostics; unprecedented TV image quality; automatic visualisation of road driving conditions; enhanced image quality in low-light conditions and improved safety on production assembly lines. The successful completion of the project has resulted in the availability of CMOS imagers that are set to replace the CCD imagers that have dominated the market for many years.

## CMOS image sensors now set to replace CCD technology

During 2011, the project worked towards the availability of full complementary metal-oxide on silicon [CMOS] image sensor designs and started the development of the final demonstrators. In 2012, the silicon for full CMOS imager designs was available and was evaluated. The final demonstrators were completed and were used to show the improved functionality that has been secured.

Research topics included pixel design and modelling, low-noise analogue read-out, including analogue-digital (A/D) conversion and multiplexing, modelling of thermal, optical and electrical crosstalk, optics and correction algorithms for CMOS imager and optical enhancement. The HiDRaLoN project focused on increasing the dynamic range of CMOS imagers to 120dB and lowering the noise level by at least 50% to make CMOS imagers better than today's charge-coupled devices (CCDs). Currently, CCDs still hold a dominant position over CMOS image sensors at the higher end of the market.

Best practices from CCD manufacturing have been retained so it is expected that the CCD imagers currently used in high-end broadcast equipment will now also be replaced by HiDRaLoN CMOS imaging devices

Functional prototypes of full imager chips for medical, broadcast, time-of-flight and machine vision were evaluated and achieved or exceeded expected results. Furthermore, all planned application demonstrators based on medical, broadcast and time-of-flight imagers were built and were fully functional.

Tests with a new industrial vision test chip proved the functionality of new building blocks and concepts and exceeded the expected results of required optical performance.

The project has delivered five new imagers for the general time-of-flight, medical, broadcast and safety/security/machine vision markets, as well as algorithms to correct flaws in the imagers and the optics. For broadcast purposes, two new lenses have been designed and evaluated together with correction algorithms designed within the project. Demonstrations in the project have focused on medical, broadcast and general three-dimensional (3D) applications.

All of the main objectives of the project were achieved and all deliverables were completed. Excellent co-operation between the partners resulted in continued co-operation even after the end of the project.

## Partners:

Budapest University of Technology & Economics

CRS iiMotion

e2v Semiconductors

Fraunhofer Institute

**Grass Valley**

Helion Vision

IMS Chips

Le2i (University of Burgundy)

Nikhef

Philips

Pilz

Technical University of Delft

**Thales**

Deutsche Thomson OHG

Viimagic GmbH

## Project leader:

Klaas Jan Damstra, Grass Valley (NL)

## Key project dates:

Start: March 2009 End: June 2012

## Countries involved:

France Germany Hungary Israel

The Netherlands

\_\_\_/

|                           | / / .    |

|---------------------------|----------|

| Communication             |          |

| Automotive and transport  |          |

| Health and ageing society |          |

| Safety and security       | V.       |

| Energy efficiency         |          |

| Digital lifestyle         | NV.      |

| Design technology         |          |

| Sensors and actuators     |          |

| Process development       | V.       |

| Manufacturing science     |          |

| More than Moore           |          |

| More Moore                |          |

| Technology node           | 45/32 nm |

## Several fields of application

While the potential range of applications for HiDRaLoN CMOS sensors is extensive, the main markets explored were medical, broadcast and industrial.

The advances obtained in the medical domain primarily involve imaging enhancements in x-ray and computer tomography (CT) equipment. The sharper images that are now possible through HiDRaLoN CMOS image sensors, greatly improve the accuracy of diagnosis to the benefit of patients and medical staff.

For applications in the broadcast environment, the first full-sized CMOS image sensors were extensively evaluated within the HiDRaLoN project. At the end of 2010, it was decided that the performance of the prototype was already so good, that it could be used to start the development of new commercial products. While the research on the CMOS image sensor continued within HiDRaLoN, parallel development continued on the first two commercial products.

There is an increasing demand and awareness in industry regarding new high dynamic range [HDR] image sensors which drive new applications or enable new image processing based systems. In addition to market reports, this is also apparent in both industry oriented and scientific conference programmes dealing with the HDR topic.

In the industrial production line environment, HiDRaLoN project developments have opened doors to considerable opportunities:

- The industrial vision image sensor developed in the project is intended to be used in new safe camera systems developments for threedimensional zone monitoring.

- Applications requiring HDR imagers, such as welding process monitor and control systems.

The main added-value lies in the reduced cost of high-performance systems.

IMS CHIPS will deliver qualified CMOS image sensors to industrial applications in Europe in volumes of up to several tens of thousands of units per year.

In addition to machine safeguarding and the machine safety market other markets with possible applications of the logarithmic industrial vision imager are:

- Intelligent video surveillance cameras

- Automotive safety systems

- Medical imaging

## Significant project outcome

The HiDRaLoN project has made a substantial contribution to the advancement of European CMOS image sensor developments. The results will have far reaching consequences for the European silicon fabs as well as for end-users in several fields of application.

All of the main objectives of the project were achieved and all deliverables were completed. Excellent co-operation between the partners resulted in continued co-operation even after the end of the project, both commercially and in terms of new European projects.

The project resulted in a long list of publications and the filing of 6 patents.

A substantial contribution was made to the EMVA1288 standard for High Dynamic Range (HDR) sensors (in version 4.0 the standard will be extended to non-linear and HDR cameras) and a Time-of-Flight Study Group was inaugurated.

One of the key factors in all CATRENE projects is the creation of a consortium of expert partners who can work together to achieve results that will advance the European strengths in various aspects of advanced technology. The CA301 project has adequately demonstrated the value of that process and the results achieved serve to illustrate the benefits.

## **CATRENE Office**

9 Avenue René Coty - F-75014 Paris - France T. +33 1 40 64 45 60

E. catrene@catrene.org www.catrene.org

CATRENE ( $\Sigma$ ! 4140), the EUREKA Cluster for Application and Technology Research in Europe on NanoElectronics, will bring about technological leadership for a competitive European information and communications technology industry.

## PROJECT RESULTS

## CA303

## Fault-mitigation electronics is the best defence against soft, firm and hard errors in critical applications [OPTIMISE]

Electronic systems deployed to control critical functions — such as in aerospace, avionics and automotive applications, as well as, in crypto-graphic chips, medical implants, networking and servers — need to be secured against errors in the information flow, and failures in electronic components. The OPTIMISE project developed optimised mitigations for advanced digital and power electronic systems that cope with the issue of reliability in the face of increasing soft, firm and hard errors.

Platforms, like satellites, launchers, aircrafts and cars, have electronic systems which are often subjected to harsh environments capable of inducing errors in their information flow, and failures in components. High-energy particles present in space, for example, cause errors and failures in space electronics. With the sharp increase in the use of computing, electronic systems, even on the ground, can be impacted. Both digital and power electronics are affected, and in the latter case, radiation can be destructive. For space, avionic or automotive applications, the mean requirement for safety critical functions is 1-10 failures in 109 hours. The answer is to develop optimised mitigations for these electronic systems in order to successfully improve reliability to counter the increasing problem of so-called soft, firm and hard errors.

## Risks assessed and mitigation techniques optimised, validated and deployed

This project had three key aims:

- To develop and validate mitigation techniques, from layout to application architecture levels, for three applications specified by different end users in automotive, avionics and space;

- To acquire knowledge on new radiation threats that may impact future electronic equipment, and work in close collaboration with standardisation bodies to propose guidelines or standards to be able to perform relevant risk assessment;

- To benefit from the synergies in the project to achieve one of the first detailed radiation risk assessments for automotive.

Validating mitigation techniques was conducted in two phases. Proof-of-concept mitigations were applied to simple test cases (such as simple test structures implemented on a test vehicle, power devices manufactured and the use of the well-known Leon soft processor) and the efficiency was then assessed based on experiments. Developed mitigations were then deployed (with some adaptation), where possible, in end-user applications, and their efficiency assessed.

Project results look promising. The proposed mitigation optimisation for the avionic system-on-chip (SoC) application passed assessment. The latest test vehicle embedding the mitigated version of the space ASIC (V53) was successfully produced in December 2013. The assembled and functionally tested parts were made available in May 2014, radiation tests and the exploitation of the results performed in June 2014, and a first assessment of the radiation risk for automotive done in 2013. In terms of product development, a new commercially available power diode (1200V SiC STPSC6H12), which offers better radiation tolerance, has been available since 2013.

In short, OPTIMISE resulted in a set of validated mitigation techniques (from layout to application-architecture levels), customised mitigations for given applications and a strong argument for standardising error assessment.

## **Close European working**

Mitigation development was achieved through the close collaboration of some 20 Spanish and French project partners, ranging from semiconductor manufacturers and their technology developers, to academic partners and end-users.

It is worth noting OPTIMISE's close interaction with RELY, a complementary project. While both deal with improving system dependability, OPTIMISE's focus is in developing mitigations for radiation effects, whereas RELY's is in the design of reliable SoCs.

## PROJECT CONTRIBUTES TO

Communication

Automotive and transport

Safety and security

## **PARTNERS**

## **COUNTRIES INVOLVED**

## PROJECT LEADER

Florent Miller Airbus

## **KEY PROJECT DATES**

July 2009 - June 2013

All partners contributed to the dissemination effort, with presentations at six events and through more than 120 publications. Standardisation was also pursued through workshops to promote tools and test methodologies and update of avionic radiation test standards. In automotive, a standardised method for assessing reliability due to radiation effects on power components was proposed.

## Impacting technology, business and safety

This project helps make possible the use of advanced electronics in critical end-user applications, and ensures the reliability of consumer electronics. Let us look at some market demands, business opportunities and benefits from which OPTIMISE's deliverables and other results can profit.

Electronics - sensors and intelligence are found everywhere in cars, increasing safety through driver assistance and drive-by-wire systems. And the allelectric car will push the use of power electronics even further. Studies show that sales of electrical vehicles have already increased by 50% since 2012. This trend is expected to continue. Now, considering reliability of electronic components is an essential element in lots of applications (including automotive domain and more particularly, power electronic applications), the number of power components is also expected to increase significantly. Similarly, SmartPower-type devices are used in many automotive power applications, also follow the same trend. Between 2005-2014, the number of SmartPower devices in a single product has increased by factor of four, and the number of products in production by about a factor of two.

A main challenge in the avionic sector is the ability to implement high performance ICs while ensuring the required safety level. OPTIMISE now offers solutions to support these and other avionics requirements. In space, satellites and launchers are totally autonomous so their reliability has to be determined prior to launch. In recent ESA space projects, complex digital and mixed signal functionalities require their integration into a single chip, making the chip size and power consumption critical for the development of the application. This also means that radiation-induced mitigation techniques, related to chip size and power consumption, also need to be optimised. Advances from OPTIMISE will allow the implementation in space chips of some functionalities that were not implementable using classical radiation mitigation techniques. Another key outcome of OPTIMISE is the development, assessment and validation of a complete 90nm digital rad-hard standard cell library.

Finally, regarding safety, OPTIMISE will provide competitive strength in sectors of European industry that need to make use of 'fail-safe' electronics in automotive, aeronautics and space applications, as well as, in those that provide enabling technology for lowpower consumer electronics. At the same it will also ensure increased human

## **CATRENE** Office

9 Avenue René Cotv F-75014 Paris - France Tel. +33 1 40 64 45 60 Fax +33 1 40 64 45 89 Email catrene@catrene.org www.catrene.org CATRENE (E! 4140), the EUREKA Cluster for Application and Technology Research in Europe on NanoElectronics, will bring about technological leadership for a competitive European information and communications technology industry.

## CA501 | Low-power design approach launches new developer Communication-centric

community

heterogeneous multi-core architectures

(COMCAS)

Mobile communications are the most important consumerelectronics market worldwide. Yet as features and customer expectations grow, they run up against the same brick wall battery life. Only by reducing power consumption can manufacturers introduce innovative new features. The challenge for COMCAS was to improve battery life significantly for small-formfactor devices by reducing power consumption. The **CATRENE** project developed new low-power approaches for semiconductor design which can reduce power consumption by a factor of five. The results are already being exploited in smartphones.

The global market for mobile devices is billions of units a year. Yet the early leadership Europe gained with the GSM mobile phone standard is under attack from Asia and its lower production costs. Innovation is considered key by European companies to maintaining market share; and for mobile devices, particularly smartphones, cutting power consumption is critical.

Such a reduction is crucial because, with a typical modern smartphone, watching a video exhausts the battery within two hours. Most consumer-electronics suppliers - as well as their customers now consider minimum acceptable battery life between charges to be seven hours, or the length of a typical working day.

The CATRENE CA501 COMCAS project aimed to improve battery life for small-form-factor devices by focusing on low-power solutions for communication-centred multi-core chip architectures. It examined the complete low-power design hierarchy, including systems-level choices, modelling of applications – algorithms and protocols – and architectures, how to maximise reuse of existing intellectual property, partitioning and mapping, virtual prototyping and minimal-power design.

## Reducing power use

COMCAS's goal was to reduce total power consumption by a factor of five while maintaining performance at current levels. It targeted 45 and 32 nm CMOS production technologies, building on the results of the MEDEA+ LoMoSA+ project which developed European low-power expertise in homogeneous architectures for mobile and multimedia. The key difference was its focus on communication-centred multi-processor architectures which require new architecture, circuit and software tools to engineer circuits with an unprecedented level of complexity.

The main design innovation was to move from a traditional performance-oriented approach to one in which performance and power consumption were considered in a more integrated manner.

Key elements were:

- Communication-centred run-time configurable heterogeneous multi-core hardware and software;

- Advanced power management at platform level;

- High-level power-estimating tools able to deliver an accuracy of within 20% of actual energy consumption; and

## **Partners:**

**ATRENTA**

AXIOM-IC

CEA-LETI

**CEA-LIST**

**CNRS [LEAT]**

**NXP** Semiconductors

Recore Systems

**STMicroelectronics**

ST-Ericsson

Synopsys

Thales

TIMA

TUD

## **Project leader:**

Armand Castillejo ST-Ericsson

## **Key project dates:**

Start: March 2009 End: February 2012

## **Countries involved:**

France

The Netherlands

## PROJECT CONTRIBUTES TO

|                          | /                                      |

|--------------------------|----------------------------------------|

| Communication            |                                        |

| Automotive and transport |                                        |

| Health and aging society |                                        |

| Safety and security      | / ]                                    |

| Energy efficiency        |                                        |

| Digital lifestyle        |                                        |

| Design technology        |                                        |

| Sensors and actuators    | -\-                                    |

| Process development      | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |

| Manufacturing science    |                                        |

| More than Moore          |                                        |

| More Moore               |                                        |

| Technology mode          | 45/32 nm                               |

|                          |                                        |

Energy-efficient devices and energy control systems

Innovative electronic design automation flow and tools

All these elements needed to be taken into account in an integrated manner if the project was to deliver a significant power reduction.

## Underpinning a community

COMCAS met its targets, developing demonstrators for four application domains – video, radio, telecommunications and advanced techniques in 32 nm – confirming the advances achieved. Two demonstrators were shown at the 2011

Nanoelectronics Forum in Dublin, where COMCAS won the first place in exhibition awards. One showed the gains from a new high-performance dual-core processor. The second demonstrator of power characterisation for a programmable architecture resulted in a significant advance for H264 kernel processing using a coprocessor-based accelerator – also known as PraXia – involving a successful collaboration between partners

Atrenta and CEA-LIST/CEA-LETI.

The dual-core chip has now been incorporated into a new kit for developers. Snowball is a low-cost, small-form-factor yet powerful mother board for fast development of mobile applications. It combines ST-Ericsson's Nova A9500 dual-core application processor with an innovative MEMS combining a 3D gyroscope, accelerometer, magnetometer and a barometer, GPS, WiFi and Bluetooth features, all in a small battery-operated device. With support for 3D graphics, high definition video and HDMI output, Snowball puts leading-edge video and mobile technologies within reach of a wider community of developers and hobbyists.

Launched at the Mobile World Congress in 2011, Snowball helps software developers to harness the capabilities of the most advanced smartphone and tablet platforms available. It is already leading developers to create applications for Android, Linaro, Meego and Ubuntu, and has given rise to its own open-source developer community, Igloo (http://www.igloocommunity.org/).

## **New market sectors**

Partner NXP has been able to develop a near-field communication (NFC) capability for a one-chip design; reduced power consumption enables the chip to handle more NFC data than earlier versions. These capabilities endow chips with important additional features; an NFC-equipped smartphone can be used to pay fares on board buses or trams for example.

NXP also joined with another company in late 2011 to release a NFC-managed online game. Skylanders, already a great success in the USA, enables gamers to keep their own personalised character and environment on a small, easily portable NFC device, and to enter or leave an online game at any location simply by passing the device through the terminal field.

COMCAS also led to several the patents — NXP filed one patent and ST-Ericsson filed two — in particular on power-efficient branch predictions and improved scalar distribution in an SMID system — while UPV filed one on on-chip communication and LEAT filed one on multiprocessor low-power schedulers.

Overall the results will help consolidate Europe's position in the aggressive and fast-growing smartphone market while enabling companies here to attack new radio and video segments — particularly video surveillance.

Finally, the COMCAS results led to a proposed new CATRENE project, BENEFIC, to determine the best energy-efficient solutions for low-power design. BENEFIC is expected to maintain the effort on power reduction through energy harvesting.

## **CATRENE Office**

9 Avenue René Coty - F-75014 Paris - France Tel.: +33 1 40 64 45 60 - Fax: +33 1 43 21 44 71

Email: catrene@catrene.org http://www.catrene.org CATRENE ( $\Sigma$ ! 4140), the EUREKA Cluster for Application and Technology Research in Europe on NanoElectronics, will bring about technological leadership for a competitive European information and communications technology industry.

# CT105 | 3D-TSV integration improves

## multimedia and mobile device applications and helps industry [3DIM<sup>3</sup>]

Cramming more electronics onto a chip, could make consumer devices, like mobile phones and tablets, even more compact, run more functions and faster, use less power and even cost less. What makes all these benefits possible is 3D integration. The heart of the 3DIM<sup>3</sup> project, this emerging technology can produce highly integrated systems by stacking them vertically (height being the third dimension, hence 3D) and connecting various materials, technologies and functional components together using a high-performance technique called TSV. This project brought together successfully European partners with specialised expertise and experience in the design and production of integrated circuits based on system-onchip and system-in-package technologies.

Deploying the technique of 'stacking', three-dimensional (3D) integration is an attractive option for many advanced consumer products. It brings together different types of chips and devices in a single package or a compact subsystem, thus gaining maximum benefit from highly specialised and heterogeneous technologies.

By replacing single-chip packages with 3D devices, higher transistor density and power savings are achieved; distances are shortened for data to travel; and manufacturing costs reduced. Key to stacking is the use of 'through silicon via' (TSV) - a chipassembly technique which impacts the overall electrical and physical design process. However, to take full advantage of 3D integration, the decision must be made early in the architecture planning process, rather than as a packaging decision after circuit design is complete.

This requires taking 3D design space into account from the start of system design in order to distribute the different components into a new set of chips that need to be stacked. However, prior to 3DIM3, there were several obstacles in the way of mass producing 3D integrated circuits. These hurdles ranged from the unavailability of proper CAD tools and a test methodology, to low manufacturing yields (thin-wafer handling process) and unacceptable reliability.

## Essential ecosystem

That is where 3DIM3 comes into its own. This project created the ecosystem that is enabling European industrials to exploit 3D stacking capabilities, by delivering all the main building blocks to start the design of a full 3D integrated system:

- TSV & TEV models and design rules

- 3D design kit

- Pieces of design flow

- 3D interconnect and protocols

- 3D test procedures

Importantly, the four demonstrators validated the 3D-TSV design flow, tools, methods, and interconnects developed during the project.

## Partner gains from co-operation

This project underscored the benefit of co-operation and confirmed what is technically and technologically achievable through such collaboration. Crucially, it switched the mind-sets of project participants to think '3D', and to start designing and verifying, complete systems with new architecture paradigms regarding standards evolution, testability, design methodologies and heterogeneous components.

Furthermore, all 14 project partners also confirmed direct benefits to their own business, or institutional activities in the case of universities. Benefits included access to advanced technology, methodologies for 3D-IC design flow and 3D-TSV tools (designing 3D circuits, for example), and the issuance of related patents.

Key partnerships were formed to establish ways of implementing the 3D chip, and to extend a leadership position in EDA methodology and tools for 3D-TSV technology.

There was also an increased understanding of TSV technology and performance, especially in RF applications; and on the process of the integration of heterogeneous technologies and to find a mixed integration solution for silicon and dies.

## Partners:

Cadence Design Systems

CEA-LETI

EADS DS

Fraunhofer Institute

Infineon Technologies

Lyon Institute of Nanotechnology

NXP Semiconductors

R3Logic

Recore Systems

STMicroelectronics

TIMA Laboratory

TU Delft

University of Erlangen-Nürnberg

## Project leader:

Virage Logic

Dominique Marron STMicroelectronics

## Key project dates:

Start: July 2009 End: December 2012

### Countries involved:

France Germany The Netherlands

## PROJECT CONTRIBUTES TO

|                          | -//-/-/-/-/// |

|--------------------------|---------------|

| Communication            |               |

| Automotive and transport |               |

| Health and aging society | /             |

| Safety and security      |               |

| Energy efficiency        | \             |

| Digital lifestyle        |               |

| Design technology        |               |

| Sensors and actuators    | -\\           |

| Process development      |               |

| Manufacturing science    |               |

| More than Moore          |               |

| More Moore               |               |

| Technology node          |               |

And with unique expertise comes competitive advantage. The acquisition of significant knowledge and understanding in the interconnectivity between the specific analogue device and the high speed processing component (decoder) strengthened one electronics company's leadership position in the home gateway market.

Academic institutions participating in 3DIM<sup>3</sup> also profited from a tight collaboration with industrial partners, and from technological advances and know-how in new packaging technologies. They were also able to set up a framework to promote future 3D research initiatives, and consolidate their leading academic position in Europe on computer architecture and embedded systems.

## Maintains competitive edge

For consumers and end-users, as mentioned earlier, 3DIM<sup>3</sup> means even smaller, faster, cheaper mobile phones and tablets that contain more functions and consume less power.

But what is the impact of 3DIM<sup>3</sup> on the industry as a whole?

Innovative 3D design solutions will enable European multimedia, mobile device manufacturers to increase the ability of their designers to build larger and better quality systems in less time and at lower costs. This means that these device manufacturers will be able to maintain leadership in this strategic market.

The know-how improvement in 3D integration will also impact semiconductor fabs [fabrication plants] by improving the production process in the near future. Critically, this project's contribution to the European knowledge will secure Europe's future forefront position in semiconductors worldwide.

The increased production of 3D devices and increasing complexity of managing the 3D products will drive widespread adoption of 3D design for mobile and multimedia devices.

Of course, it will take some time before 3D products can be massed produced, but the work and results from 3DIM<sup>3</sup> can already be used to define the architecture of highly complex products, thanks to the technological achievement this project produced in modelling, architecture, algorithms and CAD.

Most encouragingly, the design experience of 3DIM<sup>3</sup> continues to be felt through seminars and workshops, targeting European designers, with the objective of improving on the design experience 3DIM<sup>3</sup> started.

And the fact that universities are now adding 3D system design to their curriculum further confirms that 3D stacking is here to stay.

## **CATRENE Office**

9 Avenue René Coty - F-75014 Paris - France T. +33 1 40 64 45 60 E. catrene@catrene.org www.catrene.org CATRENE ( $\Sigma$ ! 4140), the EUREKA Cluster for Application and Technology Research in Europe on NanoElectronics, will bring about technological leadership for a competitive European information and communications technology industry.

# CT204 | Using smart electronics (RFID) to monitor quality of perishables (PASTEUR)

PASTEUR touches our daily lives. In helping to ensure perishables arrive at their destination in good condition, this project reduces the amount of damaged food and spoilage - an annual loss of €25 billion to the food industry and €300 to every household. Deploying sensors based on Radio-Frequency Identification (RFID) technology, PASTEUR has developed a wireless sensor platform that is able to monitor a far-wider range of environmental parameters than was previously possible, and extend environmental monitoring to crates and boxes of perishable goods along the logistics supply chain.

Central to this solution is the wireless sensor tag, based on a multi-sensor chip that connects to an RFID chip and a low-power microcontroller. This combination of technologies enables autonomous logging of the environmental conditions of products during transport and storage in the cold chain. RFID-based environment monitoring is a technology with the potential to transform the present-day supply and distribution chain. On the one hand, it will improve cold-chain distribution quality and record-keeping; on the other, it will also assist in identifying problems, assigning liability, and ensuring timely preventive measures are taken.

## Successful delivery of key technologies

The main project deliverables are several important technologies (power, sensors, wireless communication and security) key to the sensor tag and related equipment, and which were developed and integrated in a single unit. These were tested — with the help of 'demonstrators' — for integration, cost-efficiency and application relevance.

PASTEUR deals with quality monitoring of food products in two main application areas:

- Fruit: cold chain monitoring (logging of temperature and different gas fractions);

- Meat: monitoring temperature and pH (acidity or alkalinity) value after slaughtering.

Considering that these measurement systems differ widely by their very nature (measuring in gas is quite different from measuring in liquid), it was logical to define and develop two separate demonstrators:

- An integrated smart sensor tag (with temperature, humidity and possibly CO<sub>2</sub> sensor capability) for fruit (explained above);

- 2. An integrated smart pH sensor package (with temperature and pH sensor functionality) for meat.

The pH sensor consist of two components: a moulded stick (containing the sensitive pH sensor device), which is connected to a small custom printed circuit board which contains an ARM microcontroller, a battery and several other auxiliary components, including a connector for serial communication and a connector for a (optional) external reference electrode.

All deliverables successfully were tested and verified in field trials comprising a simulated cold chain, and a carcass in a slaughter house. There were also encouraging technical achievements in the deployment of active RFID labels in cold chain monitoring. Energy consumption was reduced to a low 0.5 mA (current). The tag size was kept to a compact 10 cm² and all functionality integrated in a single interface between printed and silicon element for both types of tags. In addition, a low tag price (of just over US\$ 1.00) was achieved.

## Partners:

Boschman Technologies Centro Nacional de Microelectronica (CNM)

IMEC-NL

Inkoa Sistemas

KU Leuven

Netherlands Packaging Centre (NVC)

**NXP Semiconductors**

Philips Consumer Lifestyle

Philips Innovation Services

Philips Research

Prelonic Technologies

Royal DSM

Stichting IMEC-NL/Holst Centre

TNO/Holst Centre

TP Vision

TU Delft

TU Eindhoven

Verhaert New Products Services

Wageningen UR

## Project leader:

Romano Hoofman

**NXP**

## Key project dates:

Start: July 2009 End: September 2012

## Countries involved:

Austria

Belgium

The Netherlands

Spain

## PROJECT CONTRIBUTES TO

| Communication            |                                        |

|--------------------------|----------------------------------------|

| Automotive and transport |                                        |

| Health and aging society | \\                                     |

| Safety and security      | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |

| Energy efficiency        | //                                     |

| Digital lifestyle        |                                        |

| Design technology        |                                        |

| Sensors and actuators    |                                        |

| Process development      |                                        |

| Manufacturing science    |                                        |

| More than Moore          |                                        |

| More Moore               |                                        |

|                          |                                        |

## Benefits all around

Typically, around 20% of temperature-sensitive healthcare products are wasted during transportation due to a broken cold chain. Each year, suppliers of perishables ship over five billion pallets valued at \$2.6 trillion of chilled meats, seafood, cheese, and produce, as well as temperature-sensitive pharmaceutical and biomed products.

This means everyone in the supply chain of any transported goods will benefit from PASTEUR'S technology solution: from manufacturer to transporter to retailer, and finally end-user. In the future, retailers could use this technology to install a shelf-based quality control system at sales outlets, and consumers to check (through their mobile phone) the quality of their food at home. And reduced spoilage is also good for the environment.

## European co-operation and collaboration

Key to the success of this project was the pooling together of European expertise and experience, combined with good management and communications. Crucially, the various project participants and partners contributed essential components and know-how on the different technologies in the 'value chain' of RFID-based intelligent sensor systems. Notable examples of this type of co-operation include FlexSMELL, a European project deploying RFID technology in developing an olfaction system; and Devlab in the Netherlands where wireless sensor networks are developed.

Future co-operation is also on the cards. The European project Chill-On, whose development work — combining TTI and RFID to locate and trace any food product — is of interest to PASTEUR's own R&D. Chill-On is also developing an Information Management System, similar to PASTEUR's own model, to control the parameters throughout the food supply chain. And Belgium's Flemish Institute for Logistics is also interested in collaborating in a national project.

## **Going forward**

The real attraction of the PASTEUR solution is its use of smart sensor tags in environment condition monitoring, combined with integrating multiple sensors and applying this technology solution in multi-item management, followed by item-level tagging and monitoring.

Competitive solutions in this fragmented market either offer temperature-monitoring only, or are extremely expensive and bulky, serving high-end markets (such as pharmaceuticals) or logistic bulk management (such as large shipments).

PASTEUR therefore has a competitive price-performance edge. However, it has to move fast if it hopes to get a slice of this potentially huge pie: potential competitors, who currently do not provide sensors, only wireless ICs, are quickly moving in.

One way is to approach companies are already showing interest in using the PASTEUR solution in the environmental monitoring of their supply chains. Another is to involve insurance companies, already in the logistics chain, in the smart monitoring process. Some large forwarders are already working with insurance companies to implement monitoring systems in containers. By continuously monitoring a shipment, insurers can identify the time and probable cause of damage, and, importantly, the party liable. This could even promote and facilitate the introduction of PASTEUR's technologies in cold chain management by providing a clear picture of cost and performance benefits.

The application areas for technologies developed in the PASTEUR project are not limited to the monitoring of cold chains for perishable goods. The potential variety of applications from the successful development of marketable platforms are actually quite vast. They include for example: supply chain uses such as traceability and quality management; domestic applications like detecting hazardous gases such as carbon monoxide; as well as medical monitoring to ensure therapy compliance; and corrosion monitoring for the construction industry.

## **CATRENE Office**

9 Avenue René Coty - F-75014 Paris - France T. +33 1 40 64 45 60

E. catrene@catrene.org www.catrene.org

CATRENE ( $\Sigma$ ! 4140), the EUREKA Cluster for Application and Technology Research in Europe on NanoElectronics, will bring about technological leadership for a competitive European information and communications technology industry.

# CT301 | Extreme UV lithography entry point technology development

[EXEPT]

EXEPT

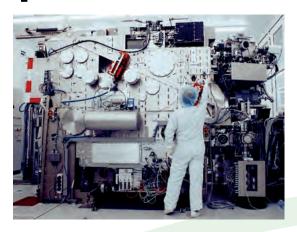

The extreme ultra-violet (EUV) lithography process is rapidly progressing as a viable production technique for less than 32nm semiconductor wafer technology. The **CATRENE EXEPT project was** set up to explore the possibilities for extending the lithography process to the 22, 16 and even 11nm nodes. The successful completion of the project now puts the European semiconductor lithography industry at the forefront of chip production expertise worldwide. During the course of the project, technology was developed to enable 22nm imaging at an acceptable costof-ownership in high-volume industrial-scale production.

## Extreme ultra-violet lithography comes of age

Over recent years, EUV lithography has gradually become the standard process used for volume semiconductor manufacturing. Through the use of double patterning technologies, it has been possible to extend the application of immersion lithography to the 32nm node. However, EUV is capable of far higher feature density and therefore allows for a greater level of functionality in a standard chip package. Consequently, the primary aim of the CATRENE EXEPT project was to develop the necessary technologies, tools and infrastructure components as required for high-volume EUV lithography for the 22 nm node while laying the groundwork for extension to 16nm and 11nm nodes.

The CATRENE EXEPT project brought together a consortium of fifteen of the leading players in the European semiconductor equipment manufacturing industry and institutes with the aim of comprehensively extending the lithography tool technology to enable imaging at the 22 nm node at an acceptable cost of ownership level for industrial chip production as well as to develop EUVL infrastructure components for which competence and an industrial base exist in Europe. With the introduction of EUV lithography for high volume semiconductor production lines, the project aims at

opening new business opportunities for the participating companies, at positioning the institutes at prominent international levels in their fields of activities and overall at safeguarding the international semiconductor industry in enabling the realization of the technology roadmap in lithography as given in the ITRS. Significant progress was already achieved on the 32nm platform in 2011 and this progress continued in 2012. Several 32nm pre-production tools are now operational at customer sites running wafers for process development. Tools were shipped employing both the laser-produced plasma (LPP) source and the discharge-produced plasma (DPP) source. Work on source debris mitigation and a collector prototype, ready for source collector module (SoCoMo) integration, has continued further outside the scope of EXEPT. This required an extension to the project in order to balance the various contributions.

## Lithography at 22nm a reality

Development of the EUV lithographic platform for high-volume manufacture (HVM) at 22nm was progressively pursued throughout the course of the 3-year project. The system performance qualification of the 22nm lithographic tool started in the 2nd half of 2011 and continued in 2012. The final

## Partners:

adixen Vacuum Products

AMTC

ASML Netherlands B.V.

Bruker Advanced Supercon GmbH

Carl Zeiss SMT GmbH

Dynamic Micro Systems

Semiconductor Equipment GmbH

FOM institute DIFFER

Fraunhofer Institute for Integrated

Systems and Device Technology

(IISB)

IMEC - Interuniversitair MicroElectronica Centrum vzw

IMS Chips

Media Lario Technologies

SAGEM Défense Sécurité SUSS MicroTec Photomask Equipment GmbH & Co.KG Xenocs

XTREME technologies GmbH

## Project leader:

Gerold Alberga ASML Netherlands B.V.

## Key project dates:

Start: March 2009 End: June 2012

### Countries involved:

Belgium France Germany Italy The Netherlands

## PROJECT CONTRIBUTES TO

| Communication            |      |

|--------------------------|------|

| Automotive and transport |      |

| Health and aging society |      |

| Safety and security      |      |

| Energy efficiency        |      |

| Digital lifestyle        | \\   |

| Design technology        |      |

| Sensors and actuators    |      |

| Process development      |      |

| Manufacturing science    |      |

| More than Moore          | V.   |

| More Moore               |      |

| Technology node          | 22nm |

milestone was achieved in August 2012. The optics for the 22nm tool are based on the development of a high numerical aperture EUV lens and the irradiation lossless illumination system, with a high degree of illumination setting flexibility. This sets new standards of excellence in the field of semiconductor lithography.

Good progress was also achieved on the development of the source collector module. Due to the huge challenges involved in developing a production-ready system of this kind, the partners also collaborated in key technology areas outside of EXEPT to ensure that the relevant enabling technologies would be available when they are needed. One example is the EUV source technology, which has to be capable of more than 100 wafersper-hour throughput.

The highly modular EUV lithographic system will allow for future upgrades and facilitates the distribution of the development work along the supply chain. Further EUV lithographic infrastructure components are developed. Those services include mask (repair and cleaning) technology and critical dimension (CD) metrology and should be seen as part of the whole EUV infrastructure.

The EXEPT project is a direct follow up to the EAGLE project (completed mid-2009), in which technologies for the EUV lithographic pre-production tool platform were developed. The EXEPT project enhances the prospect that Europe will further secure its world-wide leadership in the EUV lithography market. The project consortium members are companies from the European semiconductor equipment industry, several research institutes and a mask shop.

Most consortium members received funding from their respective national governments.

## **Ahead of Asian competitors**

Over the last few years, there has been a growing interest in EUV lithography from the integrated circuit (IC) industry. This has been demonstrated

during several conferences and in scientific publications at such events as the SPIE conferences, the EUV symposia and in several leading technical periodicals.

ASML, one of the consortium members, has already shipped six pre-production tool systems, [partly based on the technology developed in the earlier EAGLE project, with imaging capability close to 20nm] and has received 10 orders for the next generation, [the technology for which was partly developed in the EXEPT project]. The shipment of the first of these new tools was made before the end of 2012. At that moment, the fareastern competitors had not yet announced the shipment of any EUV tools.

With the completion of the project, the 22nm system is forecasted to become the first choice high-volume EUV manufacturing tool.

## Potential for further development

The work performed in the EXEPT project, as a continuation of the activities of the earlier EAGLE project, has further matured both the EUV lithography technology and the EUV infrastructure. The results of the EXEPT project have contributed to an increase of employment opportunities in the EUV ecosystem and have provided the European semiconductor manufacturing industry with a leading position in the field of EUV lithography.

The successful development of EUV technology for high volume semiconductor manufacturing has exhibited the potential to provide new fields of European expertise for application areas that will emerge in the near future. These include lithography at wavelengths well beyond those covered in this project, biomedical microscopy, metrology, the development of elemental analysis equipment and advanced research on solar energy.

## **CATRENE Office**

9 Avenue René Coty - F-75014 Paris - France T. +33 1 40 64 45 60 E. catrene@catrene.org

E. catrene@catrene.org www.catrene.org

**CATRENE** ( $\Sigma$ ! 4140), the EUREKA **C**luster for **A**pplication and **T**echnology **R**esearch in **E**urope on **N**ano**E**lectronics, will bring about technological leadership for a competitive European information and communications technology industry.

# CT302 | Towards one European test solution [TOETS]

As semiconductor chip packages become more and more complex, the process of testing gains greater significance at all stages of manufacture and throughout the lifetime of the product. The **CATRENE TOETS project was** therefore established to investigate ways of unifying test procedures both within and outside the chip circuitry and is largely based on the concepts of built-in self-test (BIST) and built-out self-test (BOST). The project consortium assembled includes several of the leading European semiconductor manufacturers and integrators as well as research institutions supporting the industry.

## A testing dilemma

The TOETS project was set up with the aim of creating a breakthrough in methods and procedures employed to test system-on-chip (SoC) and system-in-package (SiP) devices by treating the process of testing as an integral part of the whole value chain from design to application. To achieve this ambition it was essential to:

- Supply test services to the final integrator and the end-user that would be valid throughout the lifetime of the product,

- Develop chip design methodologies that provide enhanced matching of functional and test requirements, enabling a reduction in the cost of testing and achieving improved test efficiency through BIST and BOST solutions and the better use of test resources,

- Acquire relevant information about the components at transistor level to adjust performance and improve product quality.

The major goals of TOETS, that needed to be achieved by the end of the project, were targeted at improvements in dependability in application areas such as automotive and healthcare where operational integrity is essential; reducing test costs or at least stabilising the cost of testing compared to the overall cost of integrated circuit (IC) development & production and shortening test development lead times (total time to market - TTM)

## Lower costs, higher reliability

Another aspect of the project was to improve system integrity by embedding self-repair and selfcalibration features within the chip technology. Methods were developed to diagnose system issues as well as provide solutions that would compensate for faults and restore system functionality in the event of component failure. In this respect, the consortium partners also worked on different heterogeneous systems (medical, automotive, etc.) but with the same objective of reducing system test costs and improving overall system reliability.

Devices used by consortium partners to demonstrate their solutions included:

- Low cost self-test and self-calibration sensors (micro-electro-mechanical (MEM), magnetic, capacitor, temperature, etc.) embedded in a system to ensure system integrity and the highest accuracy.

- An accurate self-calibration unit for level switchers used in the functional electrical stimulation (FES) context, to guarantee optimal communication between an implant and human tissue during the entire product life.

Developments achieved demonstrate the feasibility of system-level inbuilt calibration and self-repair. An overall improvement in product quality has been shown on several systems, including those involving sensor applications. Moreover, a reduction in the cost of testing has been achieved at system level as a result of the integration of the new embedded calibration techniques.

## Reducing the cost of testing

Managing the cost of test (CoT) compared to the overall cost of chip manufacturing (CoGS, cost of goods sold) is the key to success in the very competitive semiconductor market. Consequently, the focus of the TOETS project was to develop testing

## MANUFACTURING SCIENCE

### Partners:

ATMFI

CEA-LETI

CEA-LIST

CNM-IMSE

D4T

e2v

**INESC Porto**

JTAG

KU Leuven

LIRMM

**NXP Semiconductors**

Ophtimalia

Q-Star

Salland

STMicroelectronics

ST-Ericsson

Supelec

Temento

TIMA

Tomorrow Options

University of Twente

## Project leader:

Kees Veelenturf NXP Semiconductors

## Key project dates:

Start: March 2009 End: February 2012

## Countries involved:

Austria Portugal

Belgium Spain

France The Netherlands

## PROJECT CONTRIBUTES TO

| Communication            |      |

|--------------------------|------|

| Automotive and transport |      |

| Health and aging society |      |

| Safety and security      | \\ _ |

| Energy efficiency        |      |

| Digital lifestyle        |      |

| Design technology        |      |

| Sensors and actuators    |      |

| Process development      |      |

| Manufacturing science    | V.   |

| More than Moore          |      |

| More Moore               |      |

| Technology node          |      |

methods that would contribute to cost reduction while at the same time increasing reliability.

The new device test architectures and alternative innovative test methods developed in the TOETS project provide new low-cost test solutions that allow the industrial partners to reduce their test cost, despite having only digital test equipment and by reducing test execution time per piece through higher parallelism of chip testing, even on high voltage ranges. Quantifiable and promising results have already been achieved by optimising the ratio of CoT/CoGS. Even so, there is evidently a demand for test equipment to cover the whole range of analogue and mixed signal (AMS) systems.

Currently, the only test programme generation tools available on the market are limited to purely digital test applications. None of the commercial [mostly US-based], tool vendors address the generation of analogue and mixed-signal test programmes. There are also no signs of test tool and electronic design automation [EDA] vendors indicating development plans for AMS test programme development tools. The concepts and prototypes for AMS test simulation based on defect simulation methodology, AMS/RF test programme synthesis and generation, developed in the TOETS project, will give the partners an advantage over the competition by reducing their test development time.

The computer test techniques toolbox based on statistical approaches and tools for BIST circuit evaluation will also give the partners an edge in test cost competition reducing test time and allowing low cost digital tester resources use.

## **Enhanced safety and reliability**

Overall, it can be seen that the extent of the work performed within the TOETS project has covered a very broad range of component and application areas. Specialist applications, like those used in the aviation and automotive fields, will benefit from the enhanced safety and dependency resulting from the work done during the project. Medical uses of implanted FES devices will also directly benefit from TOETS project developments that considerably enhance reliability and precision. The development of BIST and BOST techniques, together with in-built automated repair, are advances that evidently greatly increase the lifespan of components and the equipment that they support.

By working together as part of the TOETS consortium, the various partners have shared knowledge that has enabled each of them to strengthen their individual role on the world stage and, at the same time, to enhance the position of the European semiconductor industry in the highly competitive world market.

## **CATRENE Office**

9 Avenue René Coty - F-75014 Paris - France T. +33 1 40 64 45 60

E. catrene@catrene.org www.catrene.org CATRENE ( $\Sigma$ ! 4140), the EUREKA Cluster for Application and Technology Research in Europe on NanoElectronics, will bring about technological leadership for a competitive European information and communications technology industry.

# CALL 2

# CA104 | Regular array of processors boosts performance and reduces design times and costs significantly [COBRA]

Process variability, lack of flexibility, excessive designcycle times and unacceptable costs were key issues impacting conventional hardwired-based system-onchip architectures, and which triggered the COBRA project. Its objectives were to develop and experiment with an open, flexible and high-performance platform deploying a regular array of processors, and driven by automotive, radio and video benchmark applications.

At the time, excessive design cycle times — close to two years — and relatively high costs were constraining hardwired system-on-chip (SoC) architectures and their effect on marketing potential. Furthermore, process variability was not yet well addressed for 32nm nodes and smaller. At the same time, however, massively parallel processor arrays were being used in high-performance embedded systems, and for hardware acceleration in desktop computer and server applications, such as video compression, image processing, medical imaging, network processing, software-defined radio and other computer-intensive streaming media applications.

## Wide-ranging applications

With this in mind, the COBRA project was launched to define, design, assemble, and test an open, flexible, high-performance platform, based on a regular array of processors. Homogeneity was guaranteed by the architecture and by the use of a single type of processor, in contrast to heterogeneous hardware/software solutions. COBRA's main objective was to reduce the time and cost of the SoC design phase and thus provide European manufacturers with a strategic advantage.

The main result was a processing array hardware accelerator in 28nm CMOS technology that combines flexibility and performance, and which comprises four clusters comprising 17 processors. Hardware elements in this 'computing fabric' are connected through a network-on-chip (NoC) device and linked to the SoC host subsystem, together with 3D- graphics-rendering support hardware, data and instruction caches, interfaces to cameras and liquid crystal displays. This multimedia-orient-

ed demonstrator is capable of running telecommunications, video and multimedia benchmark applications. Other COBRA techniques were demonstrated on mobile telephony (such as LTE receiver/transmitter) or automotive applications (like pedestrian detection).

## Tool-kit eases and accelerates parallel programming

The COBRA platform also resolved other issues. It can control and fine-tune energy-consumption and — for a given application — help achieve an optimal power-performance trade-off. It allows for easy prototyping, especially with embedded software development: development time and effort to build and program parallel-processed applications are reduced through the use of three very fast simulation/emulation platforms — TLM, RTL and FPGA. These platforms also allow various architectural choices to be configured, tested and experimented with, largely made possible through the use of inter-processor communication that drastically increased performance.